Application G - Simulating the Impact of the Power Distribution Network (PDN) on Power Supply Systems with High di/dt Loads

To download the examples for the Applications Module, click Applications_Examples.zip.

In this topic:

G.1 The PDN Simulation Challenge

In high-performance microprocessor applications, the power distribution network (PDN) refers to the network of components, interconnections, and printed circuit board paths used to distribute power from a switching power supply source to the input voltage pins of the microprocessor load. The proper design of the PDN is vital to ensuring that the microprocessor load receives the correct voltage and current over all operating conditions, including during current steps on the order of 1000 A and slew rates on the order of 1 A/ns.

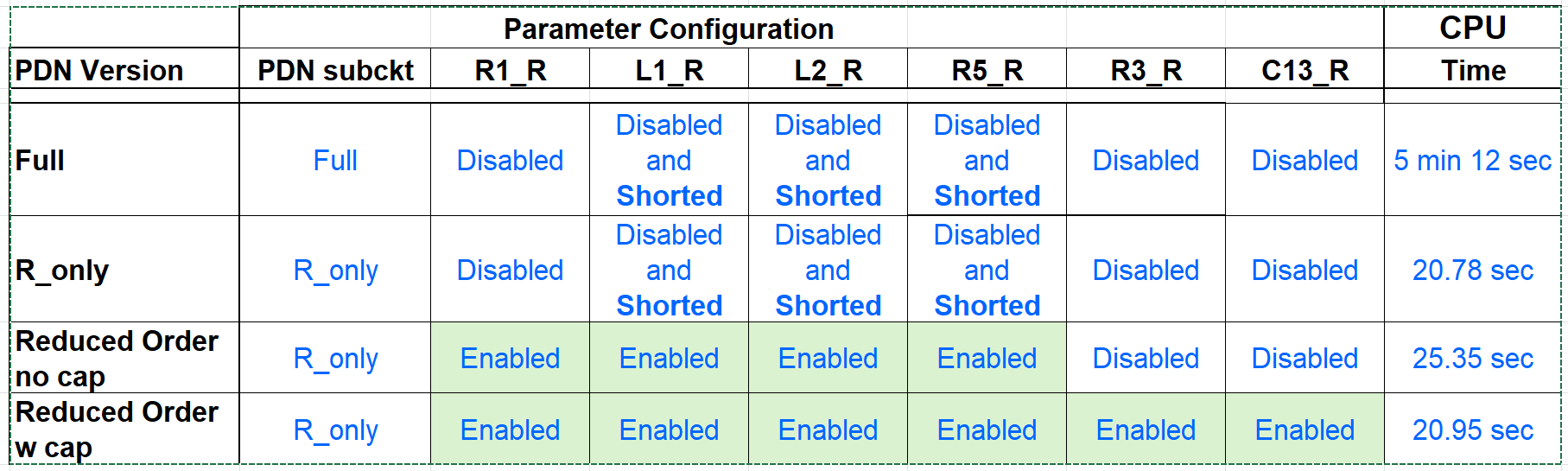

|

||

|

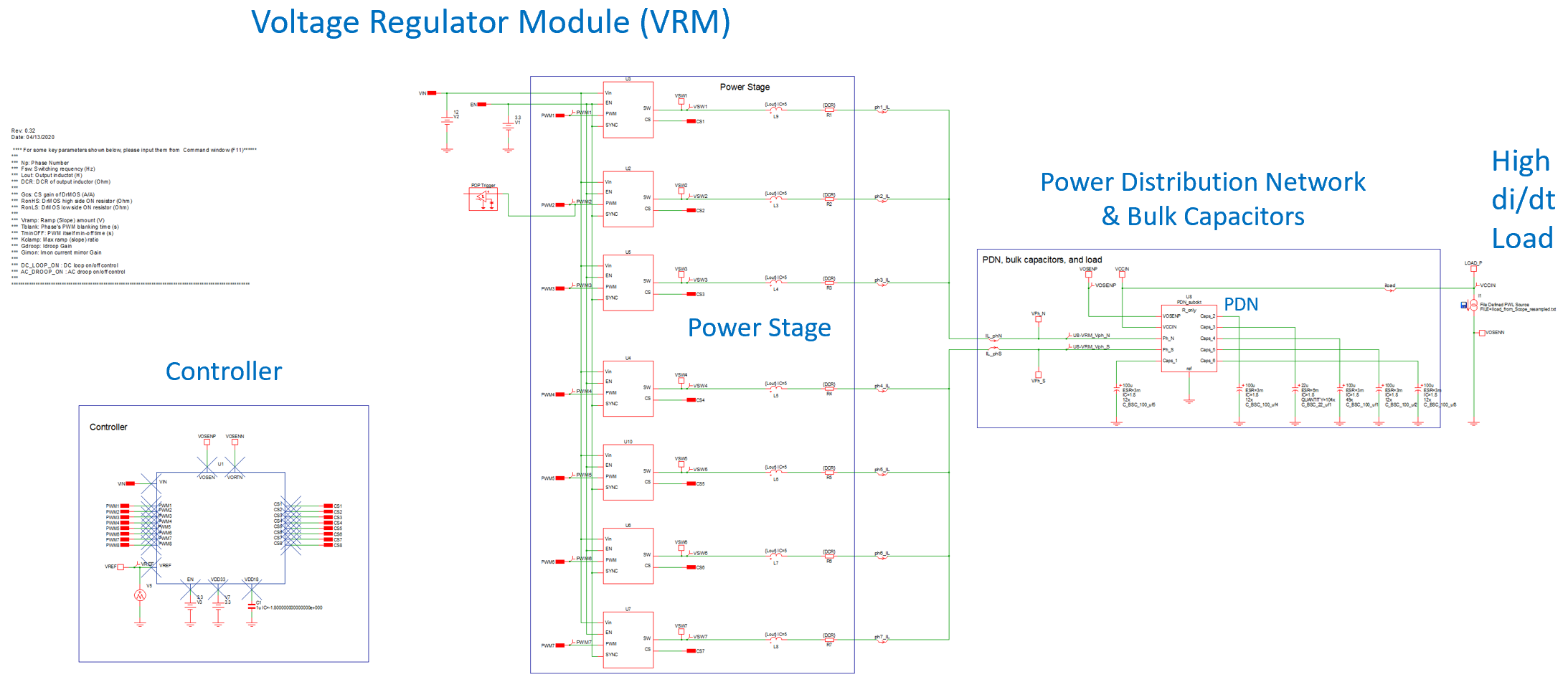

Figure G.1: Critical elements of a Voltage Regulator Module include the Controller, the Power Stage, the Power Distribution Network and the discrete bulk output Capacitors. |

||

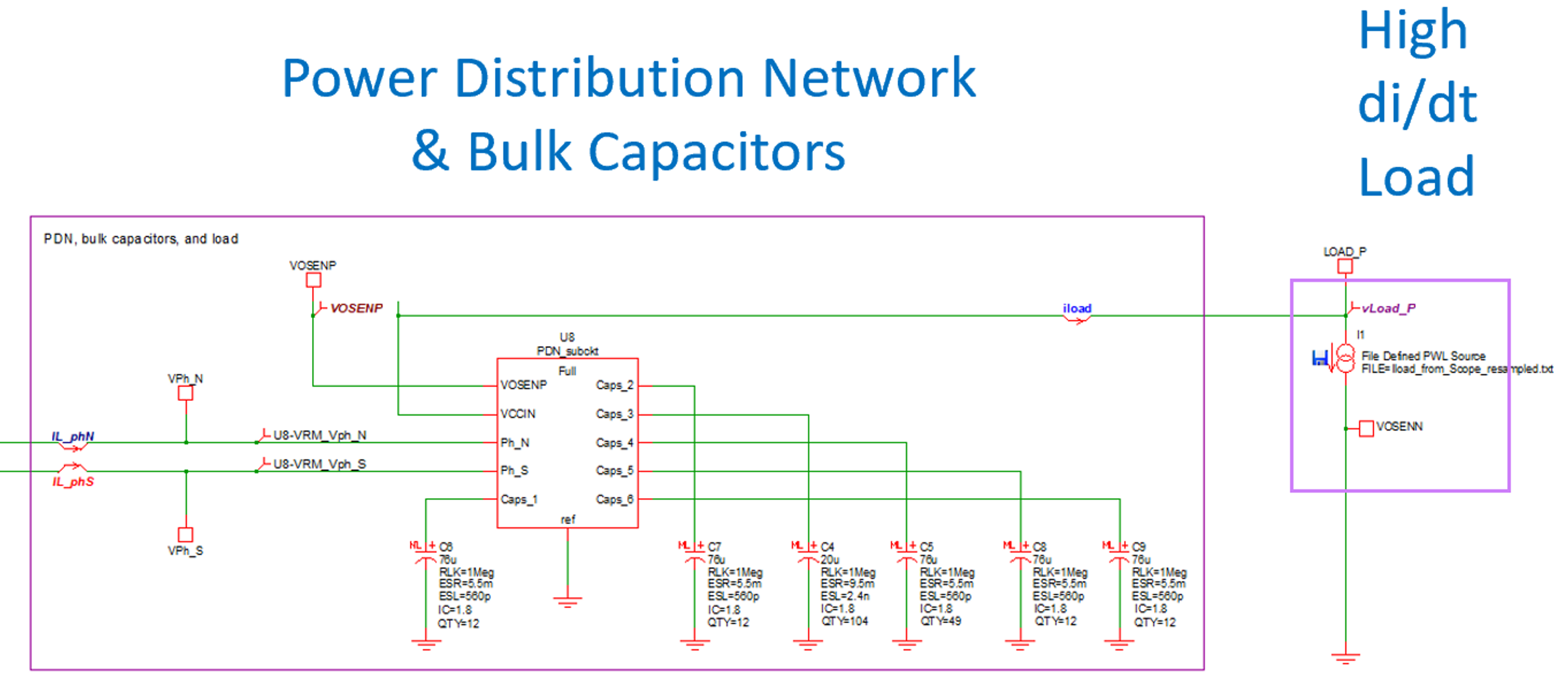

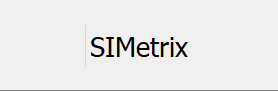

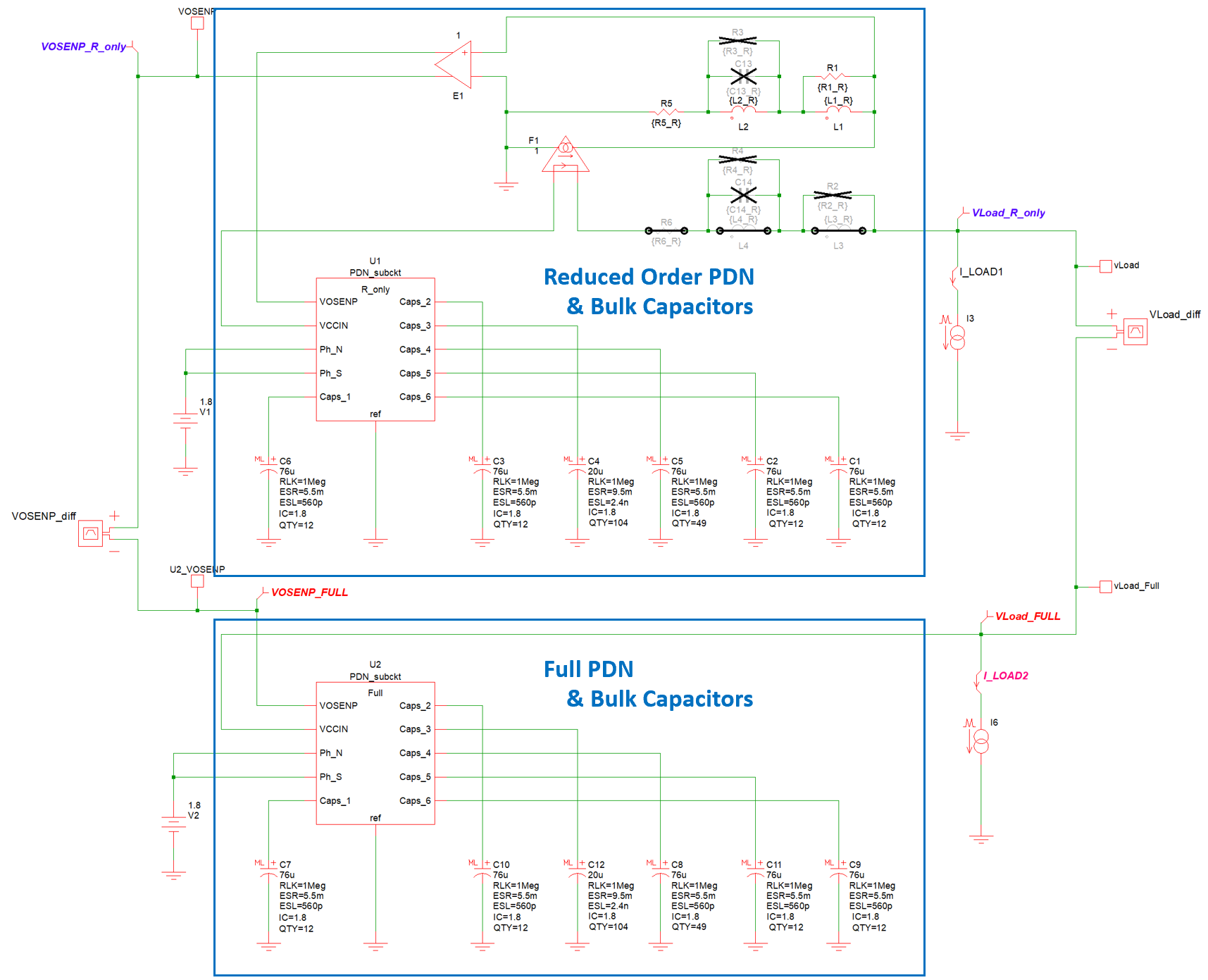

Figure G.1 illustrates the top-level schematic of the working example used in this analysis showing the Voltage Regulator Module (VRM) made up of an IC Controller and the Power Stage of a 7-phase Synchronous Buck DC-DC Converter. The 7 output inductors of the power stage are connected via the PDN to the input terminals of the microprocessor load. The bulk energy-storage output capacitors are connected in parallel at multiple points along the PCB paths between the output inductors of the power stage and the input terminals of the load.

This VRM is designed to deliver power to high current loads with very high di/dt requirements such as high-end microprocessors. Central to the converter's operation is the controller, which persistently senses fluctuations in output voltage and adjusts the duty cycle of each phase of the converter Power Stage to maintain a constant voltage at the load. This Voltage Regulator Module (VRM) efficiently steps down an input voltage to meet the specific output voltage requirements of the load. Additionally, bulk energy-storage output capacitors are included within the system to provide energy to the load during severe load transients when there is a large mismatch between the instantaneous load current and the instantaneous output current of the power stage of the VRM.

The core focus of this study is the Power Distribution Network (PDN), particularly the impact of the parasitic components contributed by the layout of the Printed Circuit Board (PCB) on power quality delivered to the load during high di/dt events. These parasitic elements, intrinsic to the physical design of the PCB, include parasitic resistances, inductances and capacitances which can have a non-negligible influence on the voltage delivered to the load.

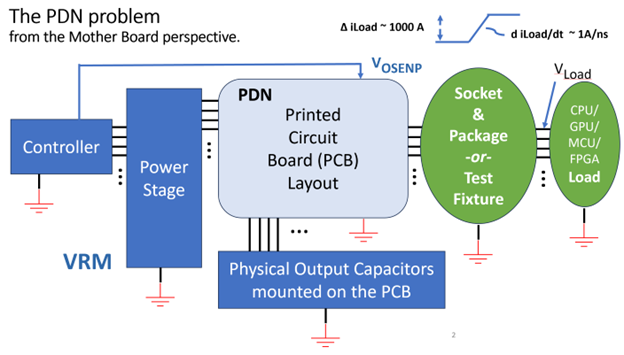

In this analysis, we examine the PDN design challenge from the perspective of a Mother Board designer. In this case, the mother board designer is responsible for the design of the VRM and the PCB layout. The socket and package containing the processor load are givens in this design.

In this analysis the PDN block only describes the PCB parasitic elements that define the impedance between the output inductors and the load, and model the physical location of the connections to the discrete bulk capacitors. These discrete bulk capacitors are shown as external components and are explicitly not included in the PDN. This allows us to isolate the effects of the PCB layout parasitics on the performance of the power system from the impact of the number and quality of the bulk capacitors when handling the dynamic power demands of microprocessors with extremely high di/dt load transitions.

While in the final product the mother board designer will be concerned with the socket and IC package, often during the early design phase, a PDN model for the socket and package is not be available. In these cases, there will be a Test Fixture that will be specified so that if the output voltage excursions as measured at the VOSENP pin of the test fixture meet the system requirements, then the designer can be confident that the end product will likewise meet the power system requirements.

In our study, we have a PDN model of a Test Fixture that has been combined with the PDN of the PCB. So, while we can predict the voltage vLoad_P, it is modeling the voltage at the point where the load is connected to the test fixture. So, we can expect that the voltage VOSENP will accurately approximate what we will see in the final design, the voltage at vLoad_P of the test fixture will have more series parasitic inductance to contend with than we expect to encounter in the actual connection to the input voltage pins of the microprocessor chip in the final design.

We note that while it is possible to include the discrete bulk energy-storage capacitors within the PDN for some analytical purposes, such an approach is not compatible with the procedure presented here for addressing the PDN challenge. In this procedure, it is important to exclude from the PDN all discrete capacitors that are mounted on the PCB. As a result, the PDN represents only the parasitic impedances of the PCB, and the bulk capacitors are represented as discrete components on the top-level schematic.

As we can see in this figure and in Fig. G.1, the controller has two pins VOSENP and VOSENN that are used to make a kelvin connection to the package through the socket. These pins are as close as the designer can get to actually measuring the input voltage to the die inside the IC package. Consequently, all specification requirements that the mother board designer must meet are referenced to these VOSENP and VOSENN pins. In this analysis, VOSENN is connected to node zero ground, so we can sharpen our focus to just the VOSENP pin when we want to verify that the voltage requirements of a particular load have been met under various critical operating conditions.

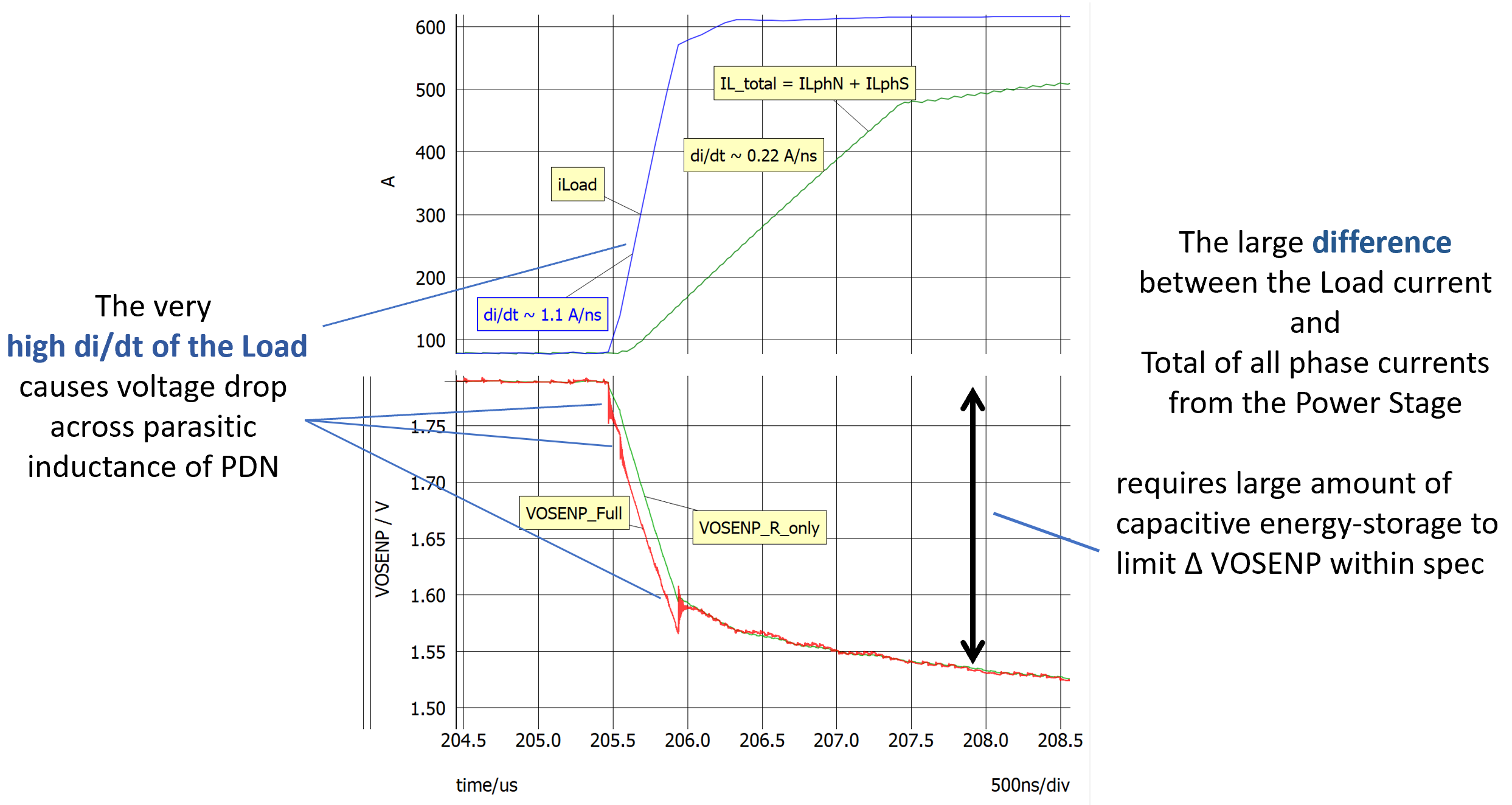

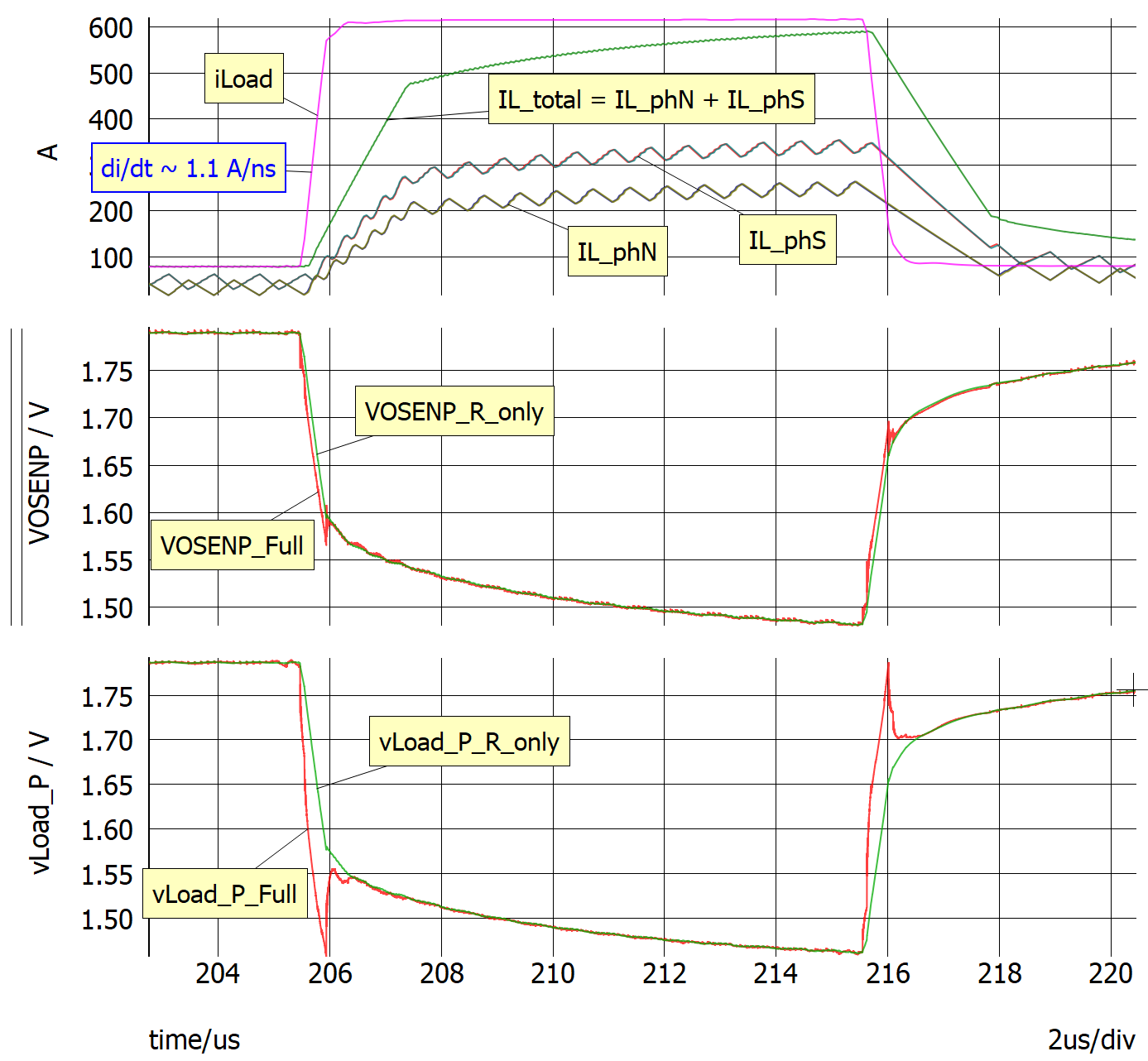

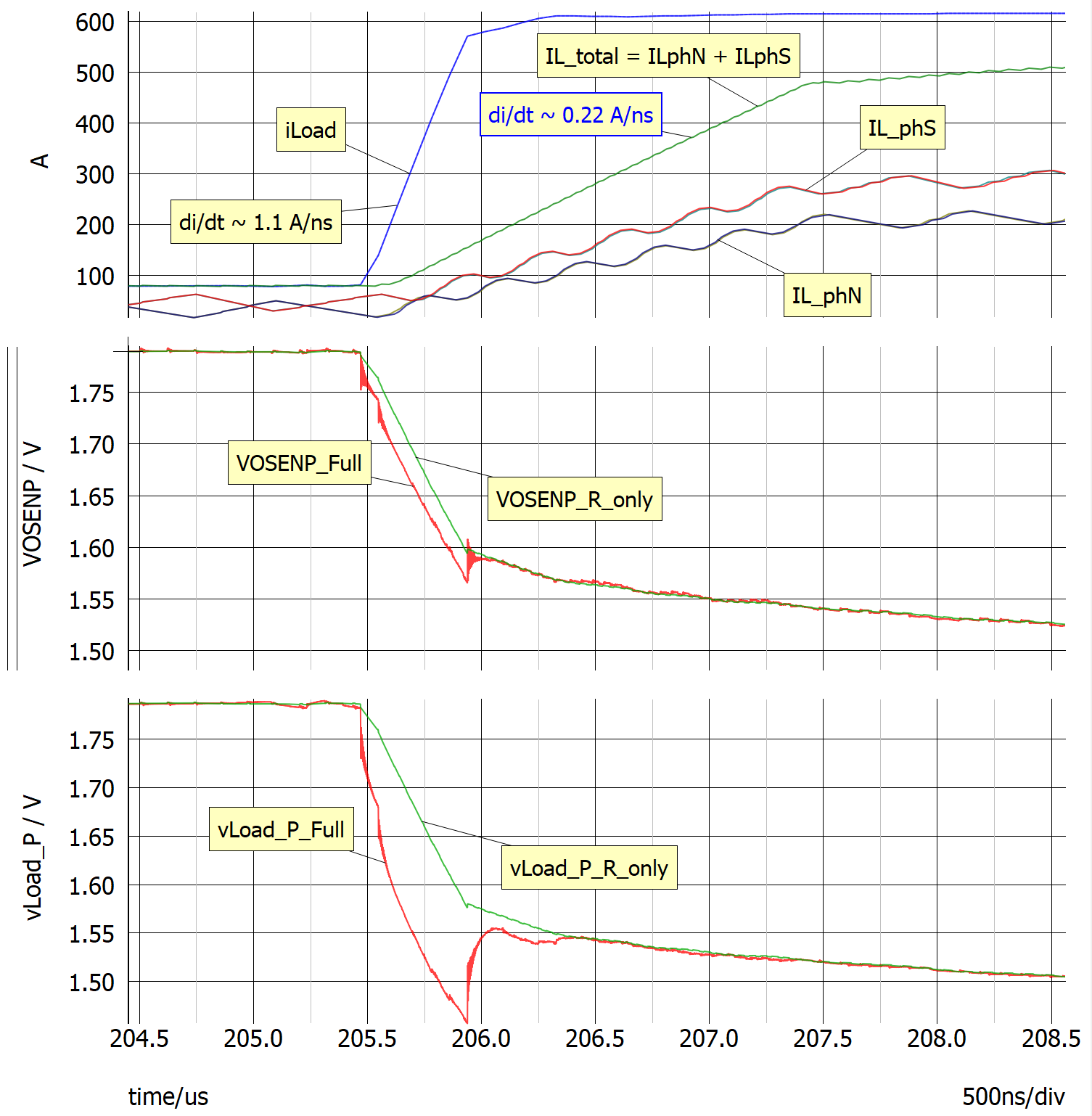

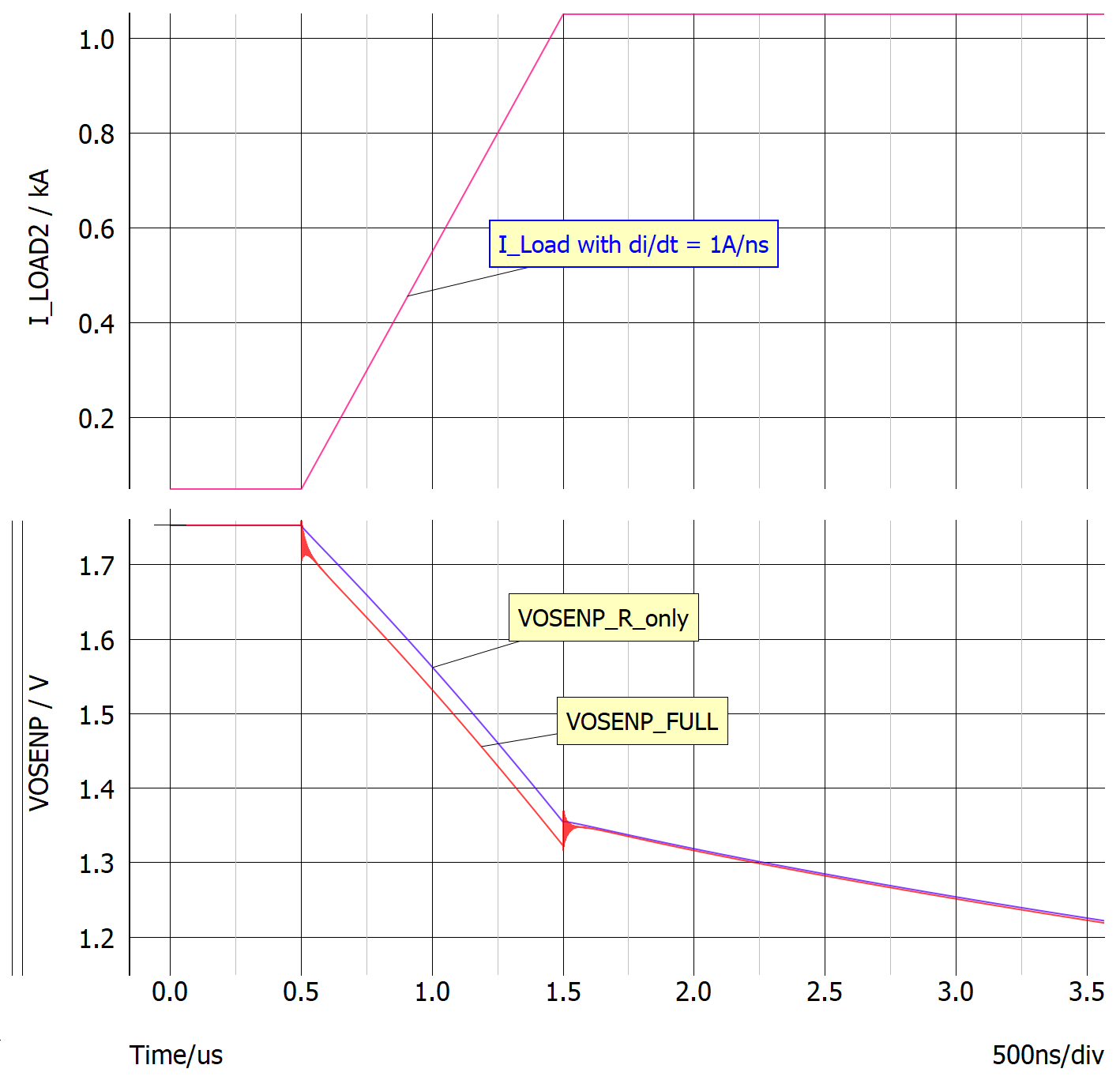

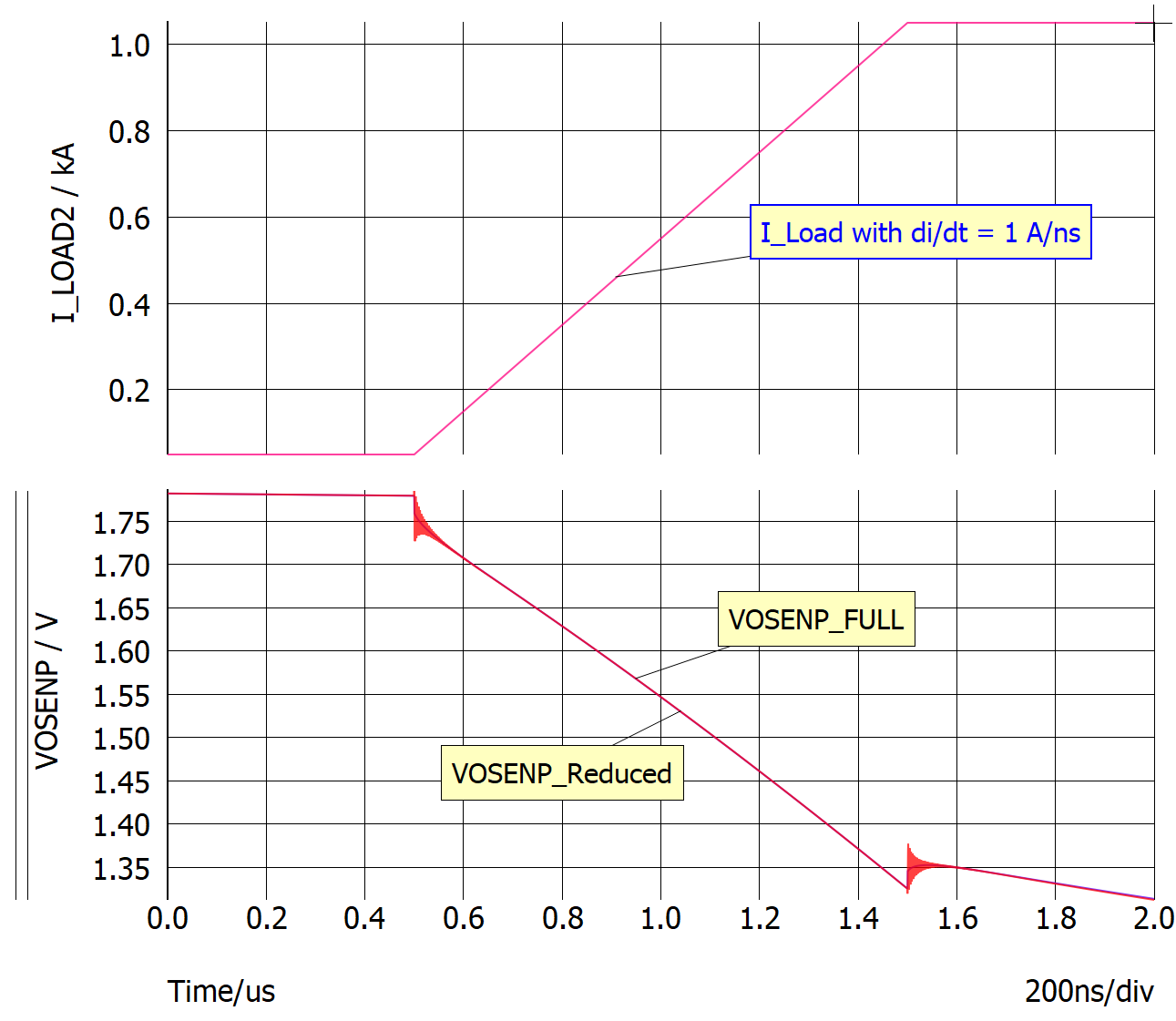

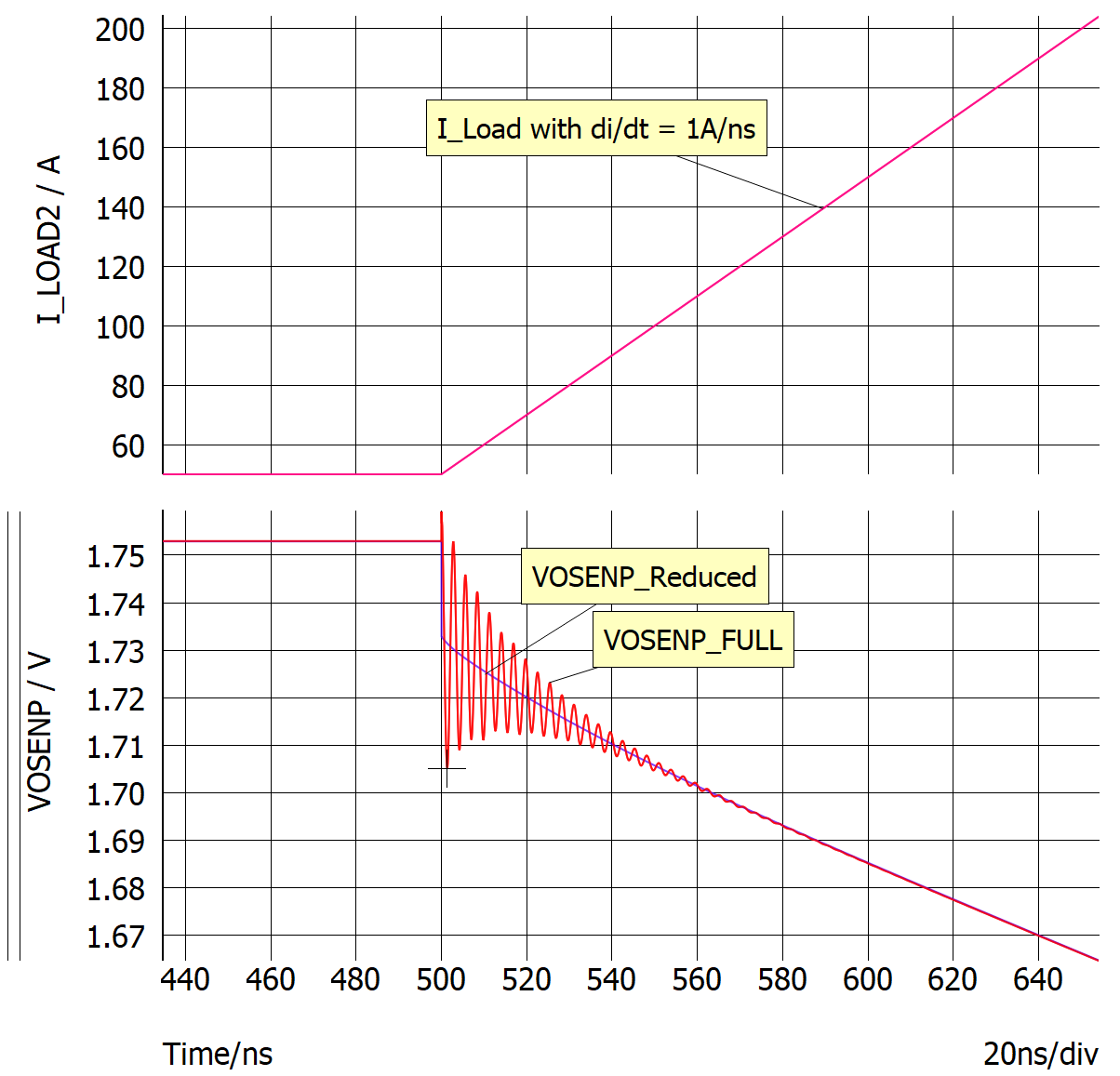

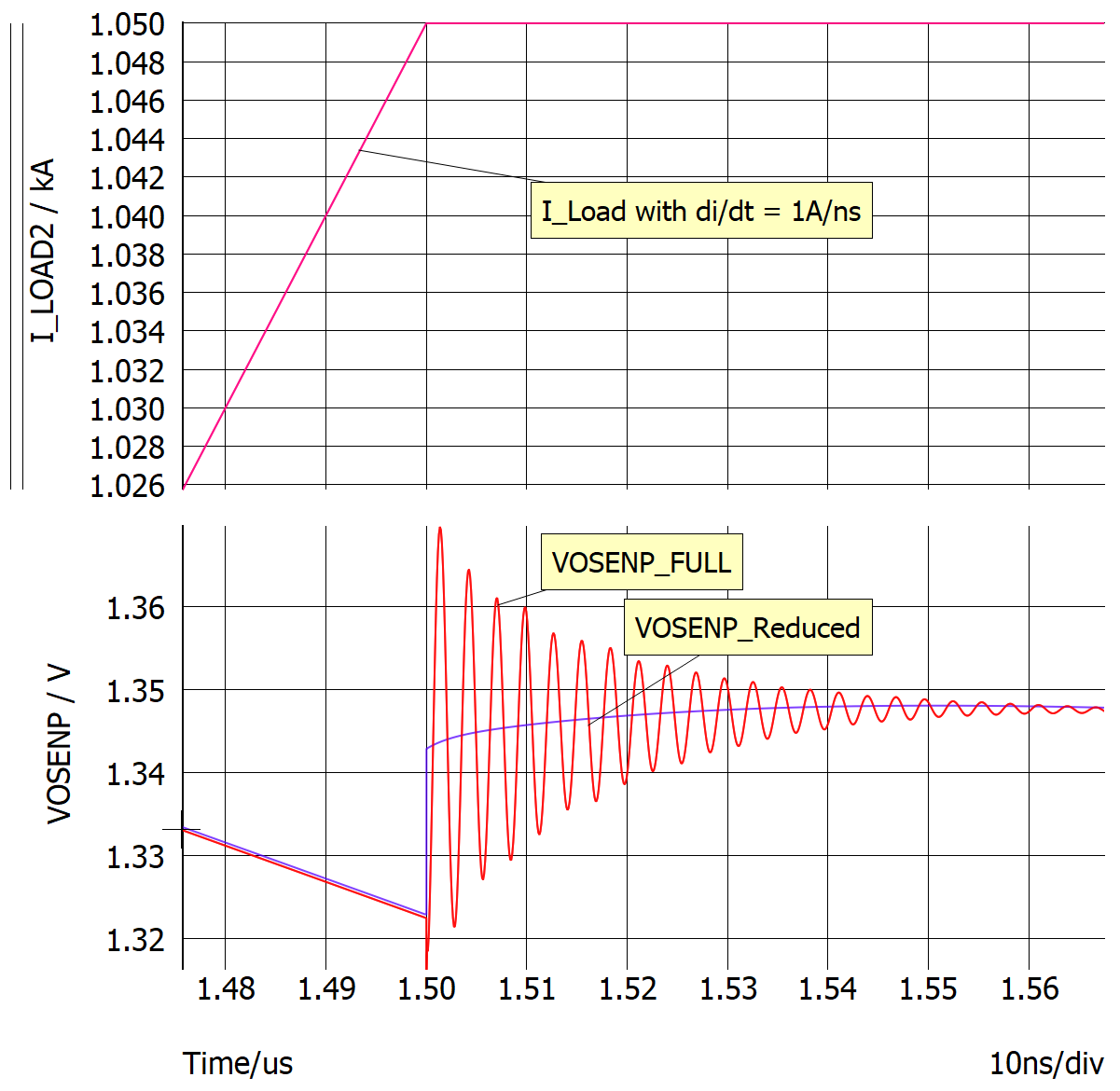

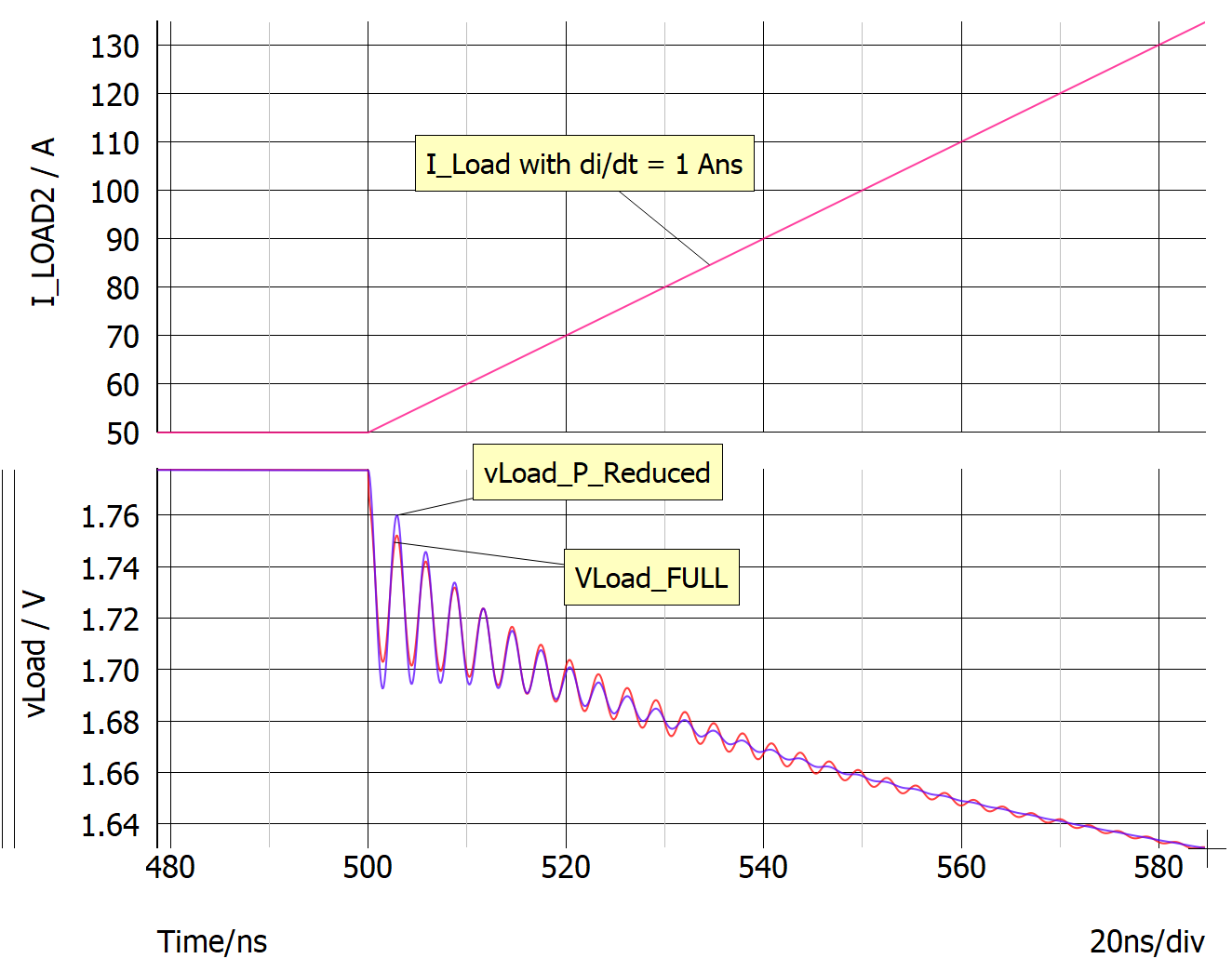

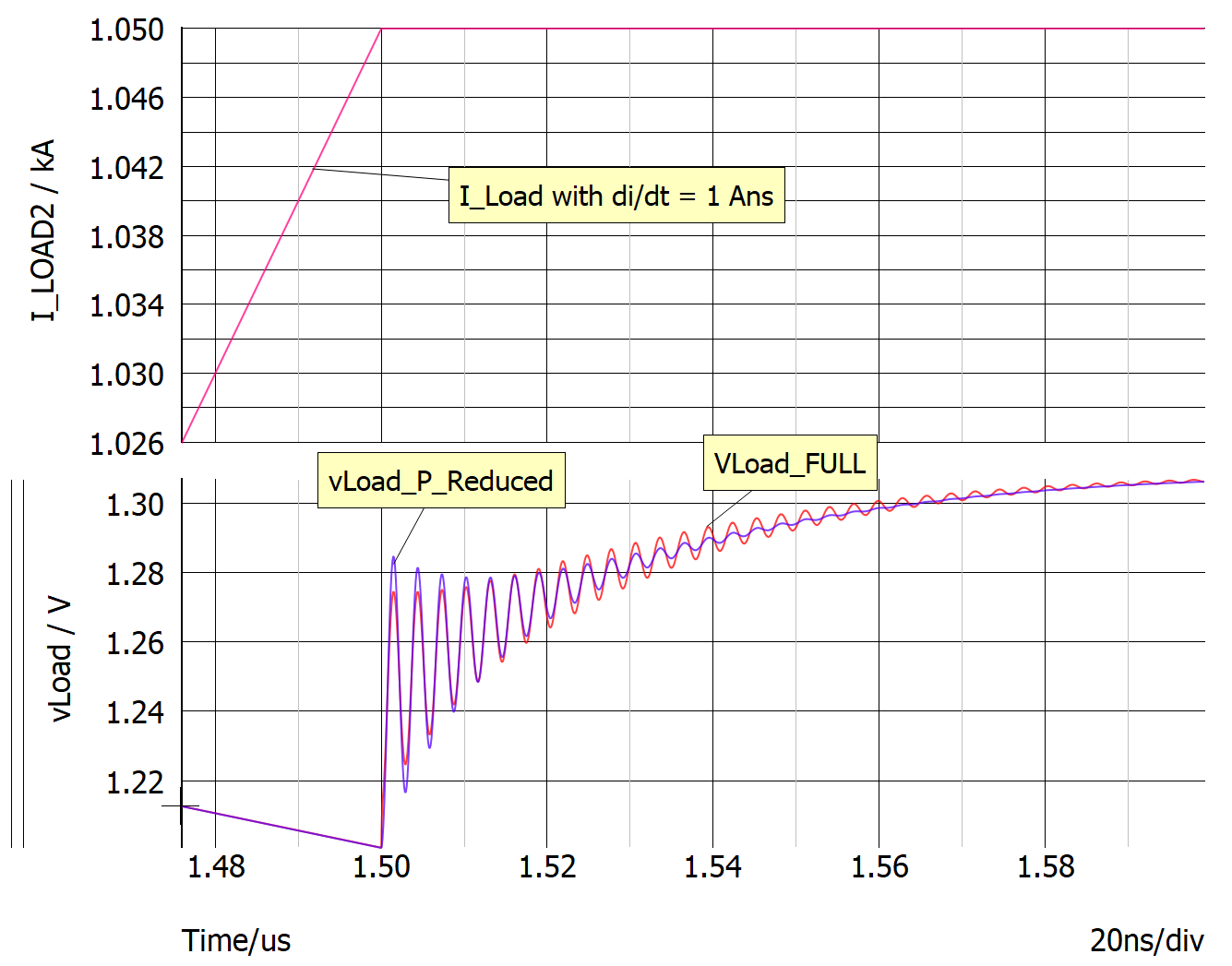

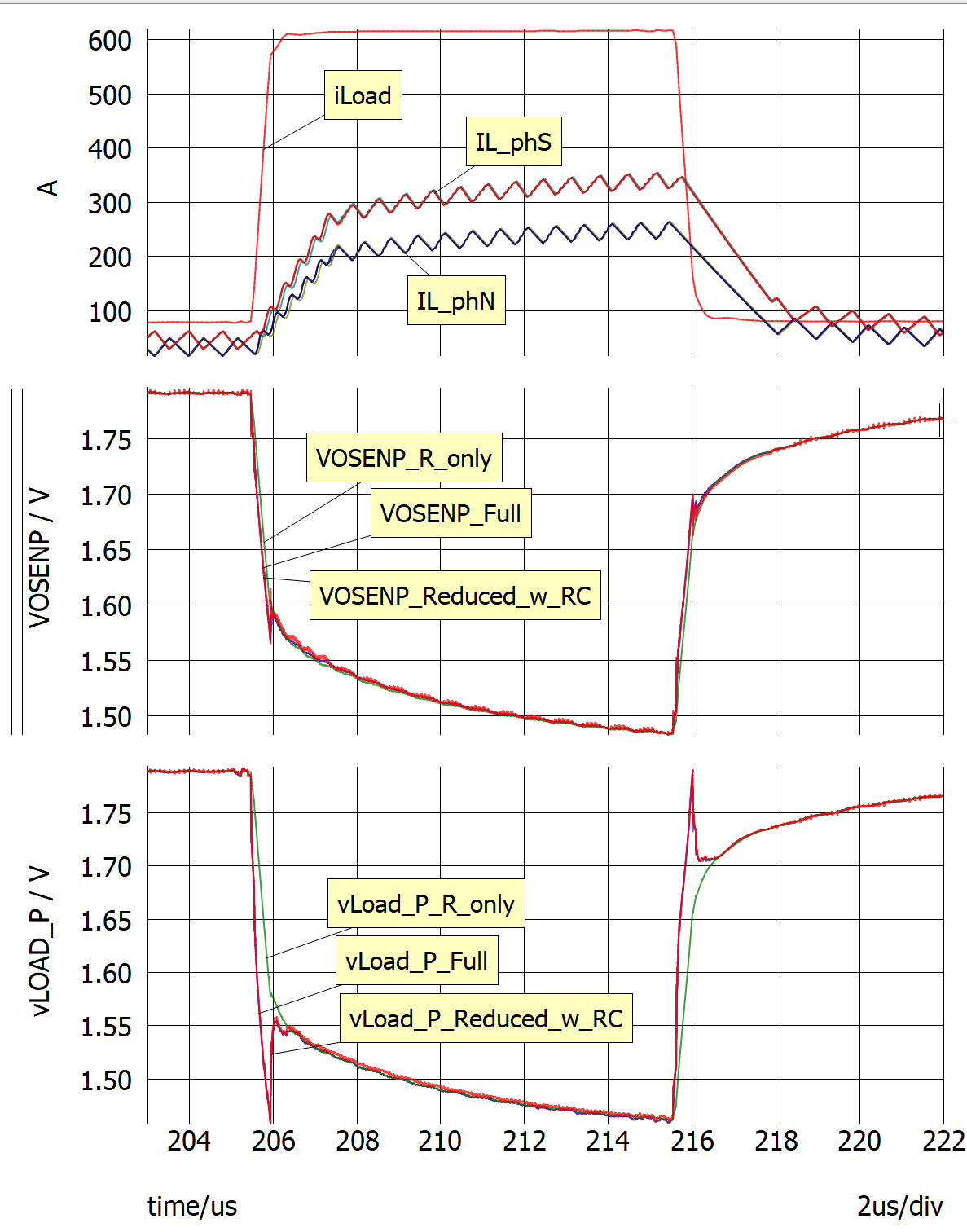

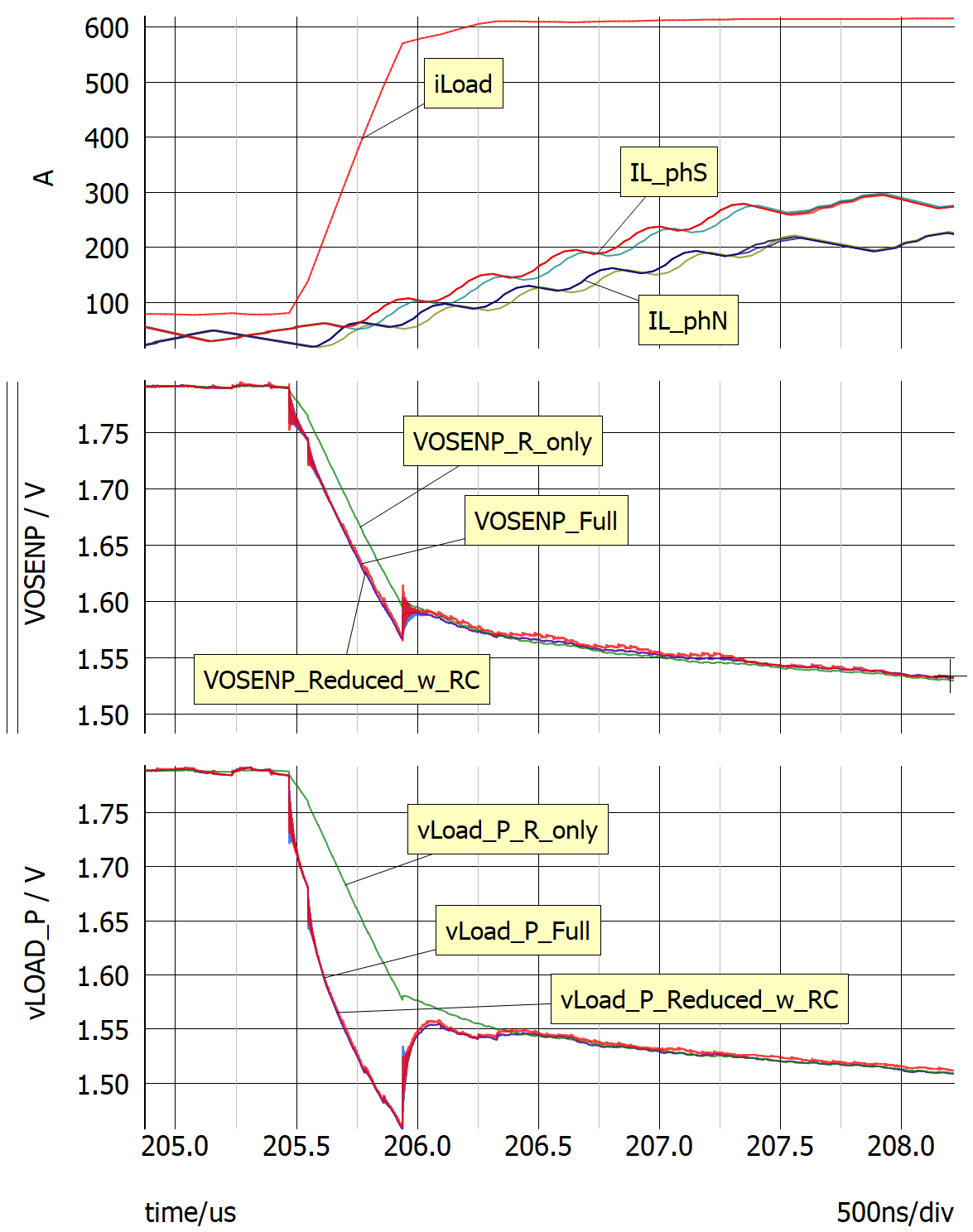

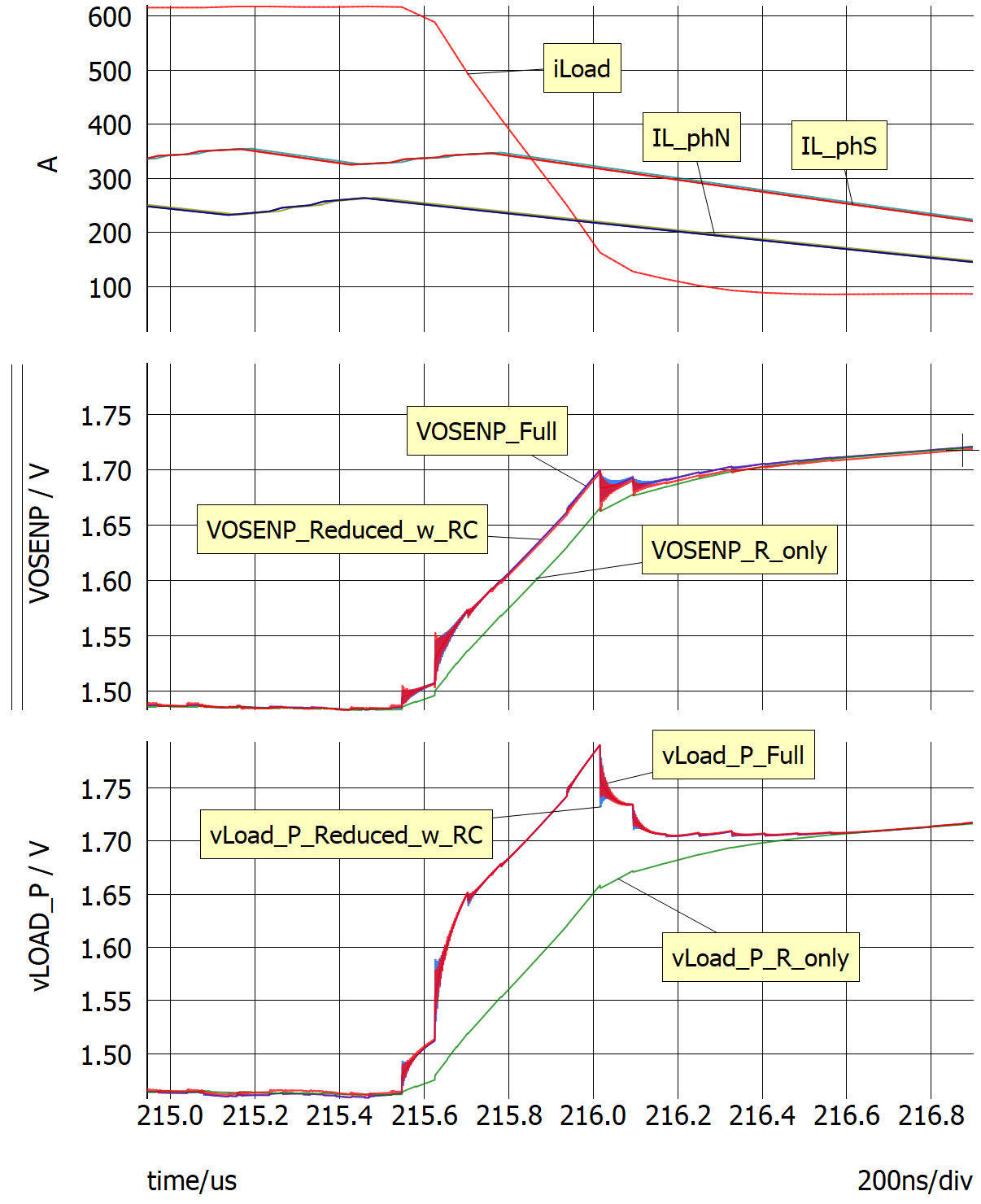

Figure G.2 illustrates the importance of being able to simulate the performance of the VRM with its associated PDN when powering very high di/dt microprocessor loads. In the top grid we see the load current iLoad transient rising from ~ 80 A to ~ 613 A with a rise time of approximately 1.1 A/ns. Superimposed on that curve is the sum of all the output inductor currents iLtotal which equals the sum of the three phases iL_phN being fed into the “North” side and the 4 phases iL_phS being fed into the “South” side of the microprocessor package. We can see that the VRM is not able to ramp up its total output current iLtotal nearly fast enough to match the load. In fact, during this step load transient, the load current exceeds the total current iLtotal coming from all the output inductors by as much as 400 Amps. The load current, iLoad, exceeds iLtotal by more than 50 Amps for more than 6 μs. In order for the input voltage to the microprocessor not to dip too much during this transient this excess load current must be supplied by the bulk capacitors. To do this successfully the ESL and ESR of the bulk capacitors as well as the parasitic inductance and resistance of the connection introduced by the PCB layout must be managed very carefully.

|

||

|

Figure G.2: The VOSENP pin to the controller is used to sense the input voltage ot the microprocessor shown here under a high di/dt load transient. Waveform VOSENP_Full shows effect of parasitic resistance, parasitic series inductance, and parasitic capacitance of Printed Circuit Board (PCB) layout (PDN) under a step load of ~530 A with slew rate of ~1.1 A/ns. VOSENP_Full shows the combined effects on the sense pin VOSENP voltage of all parasitic elements of the PDN. VOSENP_R_only shows the effects of only the parasitic resistances of the PCB layout or PDN. |

||

On the lower grid of Fig. G.2 is a plot of two curves. The curve labeled VOSENP_Full shows the sense pin voltage for the microprocessor during this load transient with the full model of the PDN that includes all the parasitic resistances, inductances and capacitances of the PCB layout. The curve VOSENP_Ronly shows the resulting sense pin voltage waveform if only the parasitic resistances of the PDN model are included in the simulation. The difference between these two curves shows the impact primarily of the parasitic inductances of the PCB layout. The impact of the PCB parasitic capacitances is relatively minor for our purposes. These two curves diverge when there is a significant di/dt of the load current. Otherwise, these two curves are very close to each other. There is a small amount of ringing where the parasitic capacitance interacts with the parasitic inductance during significant changes in di/dt of the load current.

Remote sensing has long been used to compensate for resistive drops between the output of a power supply and the load. However, with the extremely high di/dt load transients of recent generations of high-performance microprocessors, the inductive impedance of the PDN can no longer be ignored.

During these severe load transients with di/dt ~ 1.1 A/ns, to meet the regulation requirements, the sum of all the effective series inductances between the output bulk capacitors and the input terminals to the load must be kept to a value on the order of 0.1 nH. This challenge to deliver on the order of 1000 A through a PDN with less than 0.1 nH of ESL is a bit breath taking and not for the faint of heart. It is not hard to understand why simulation tools are essential to master this design challenge within a time frame compatible with today’s very short development schedules.

When powering modern high performance microprocessors, the PCB layout and the placement, quality, and quantity of the bulk capacitors has become a critical dimension of the power supply system design. The design of the PDN has become too important and too sensitive, and the development schedules have become too short to be supported solely by trial-and-error design methods. Here we demonstrate a procedure to apply Power Supply System simulation to verify that a given Power Supply design with a given PDN will meet system requirements.

To accomplish this goal, we need a detailed simulation model of the VRM controller of Fig. G.1. To handle the demanding requirements of this application, these controllers typically employ highly nonlinear control strategies to handle the high di/dt load transients. They also will often shed phases of the Power Stage under very light load conditions to reduce power dissipation and improve operating efficiency at light loads. Consequently, these VRM simulation models can be very complex. In order to model these severe load transients these models must be time-domain switching models. Averaged models cannot accomplish this task.

We also need accurate simulation models of the PDN. Current methods to extract a Spice model of the PDN use PCB analysis methods that were originally created to address signal integrity applications for high-speed digital signals flowing through narrow PCB traces. These tools have now been adapted to analyze the PDN. Depending on the upper frequency of the requested analysis, the resulting simulation models can be quite complex as they attempt to model effects in the 10 GHz range. These high frequency PDN models can have more than 3000 to 4000 poles or similar number of equivalent inductors and capacitors. PDN models this complex will result in SIMPLIS system simulations that are impractically slow when considering the number of system simulations that must be completed in a reasonable time to meet ever shortening project schedules.

Fortunately, these extremely high frequency models are not needed to achieve accurate simulation results. Here we demonstrate how a simplified lower order model of the PDN can achieve very useful results with much faster simulation times that are compatible with demanding project schedules.

G.2 Overview of PDN Analysis Procedure

Here we present the outline of the PDN Analysis Procedure that we recommend addressing the PDN challenge described above.

- Extract Spice netlist of PDN from PCB layout

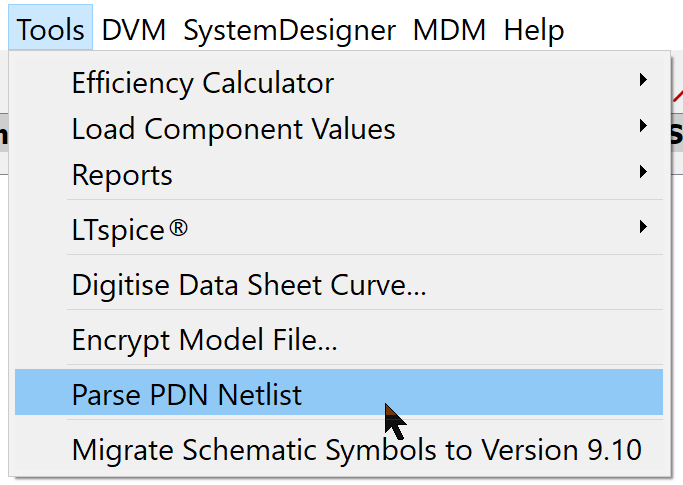

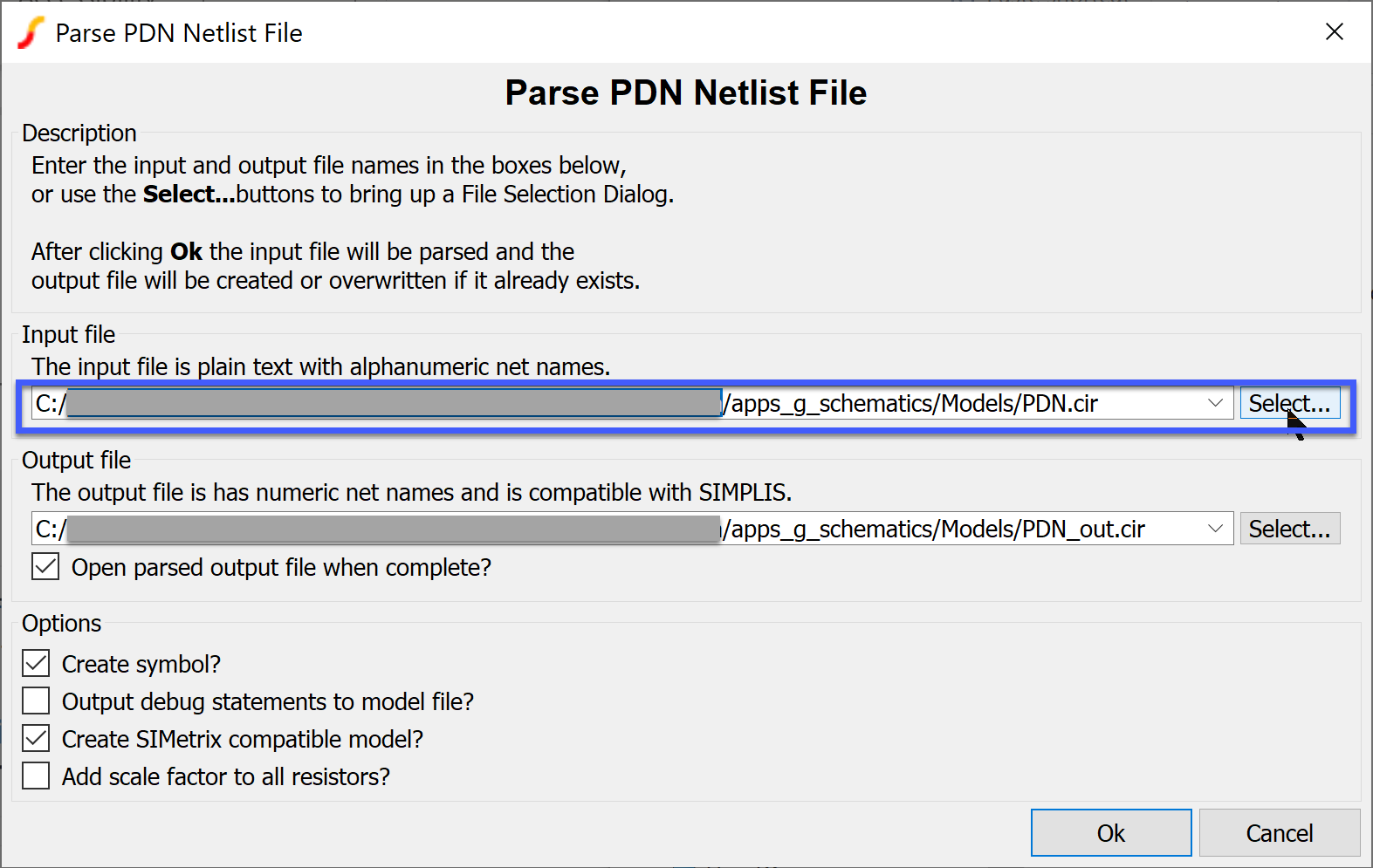

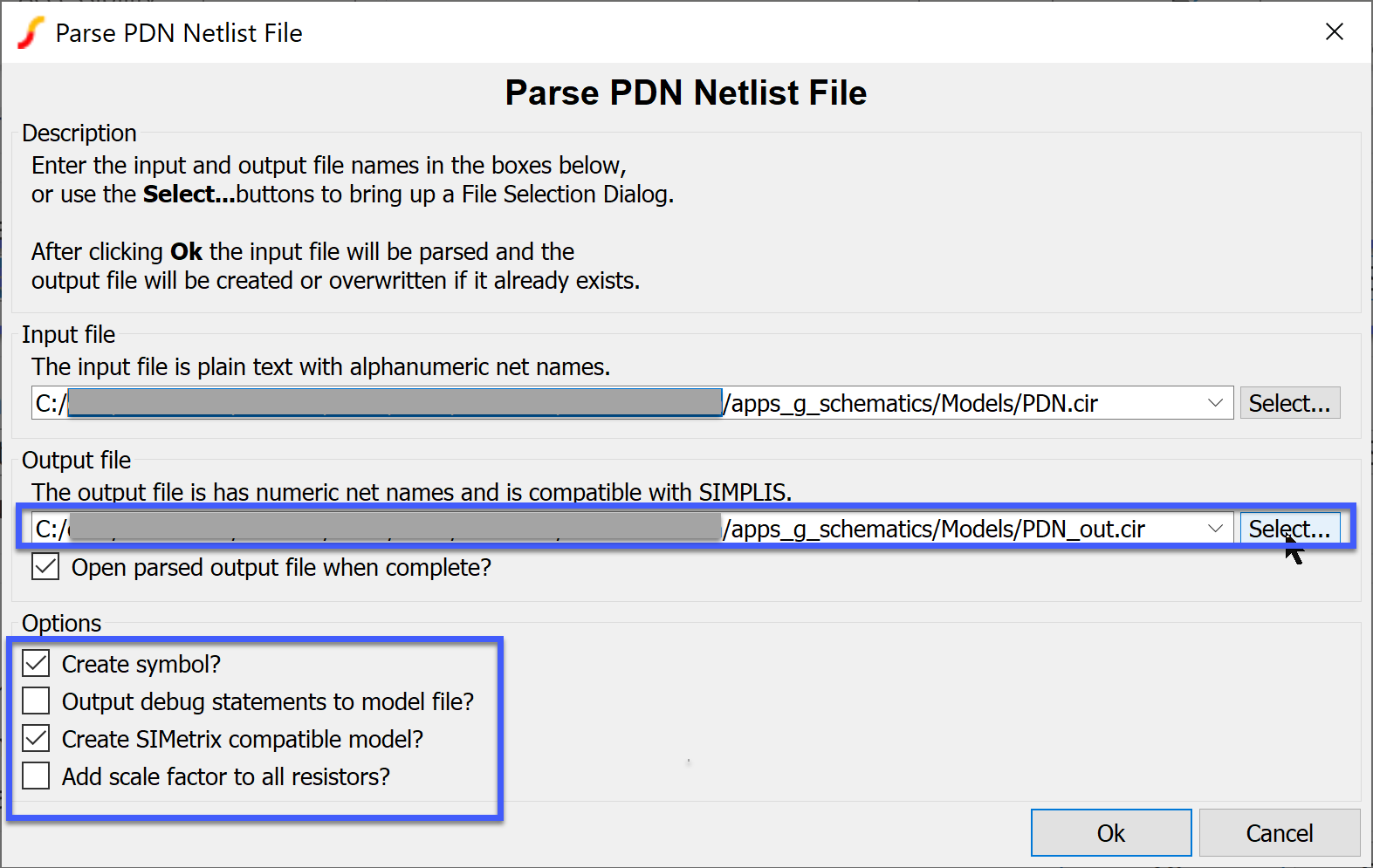

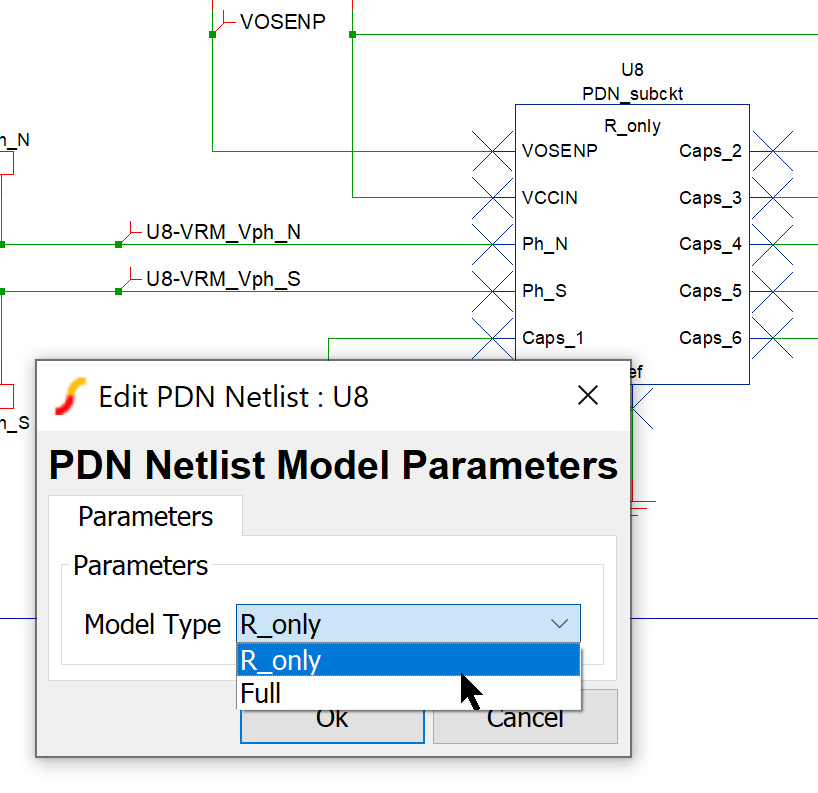

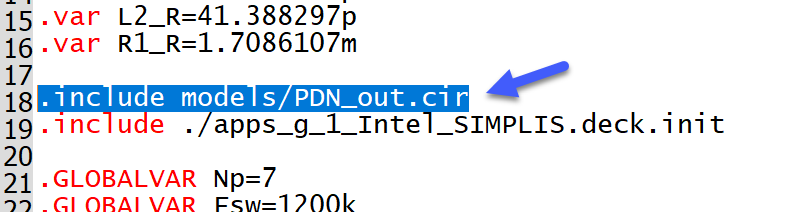

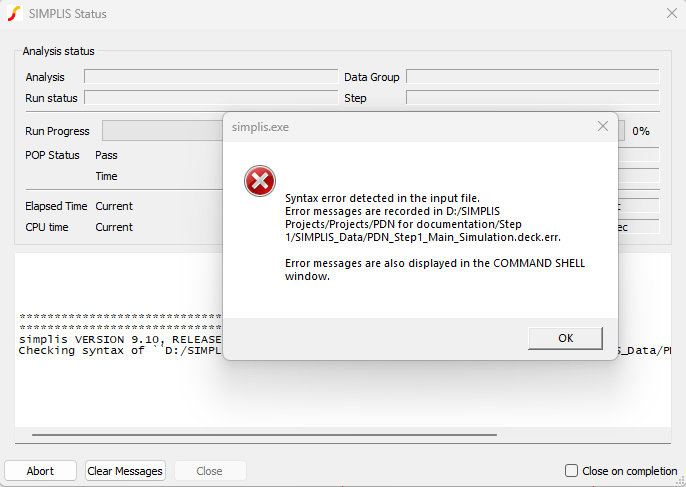

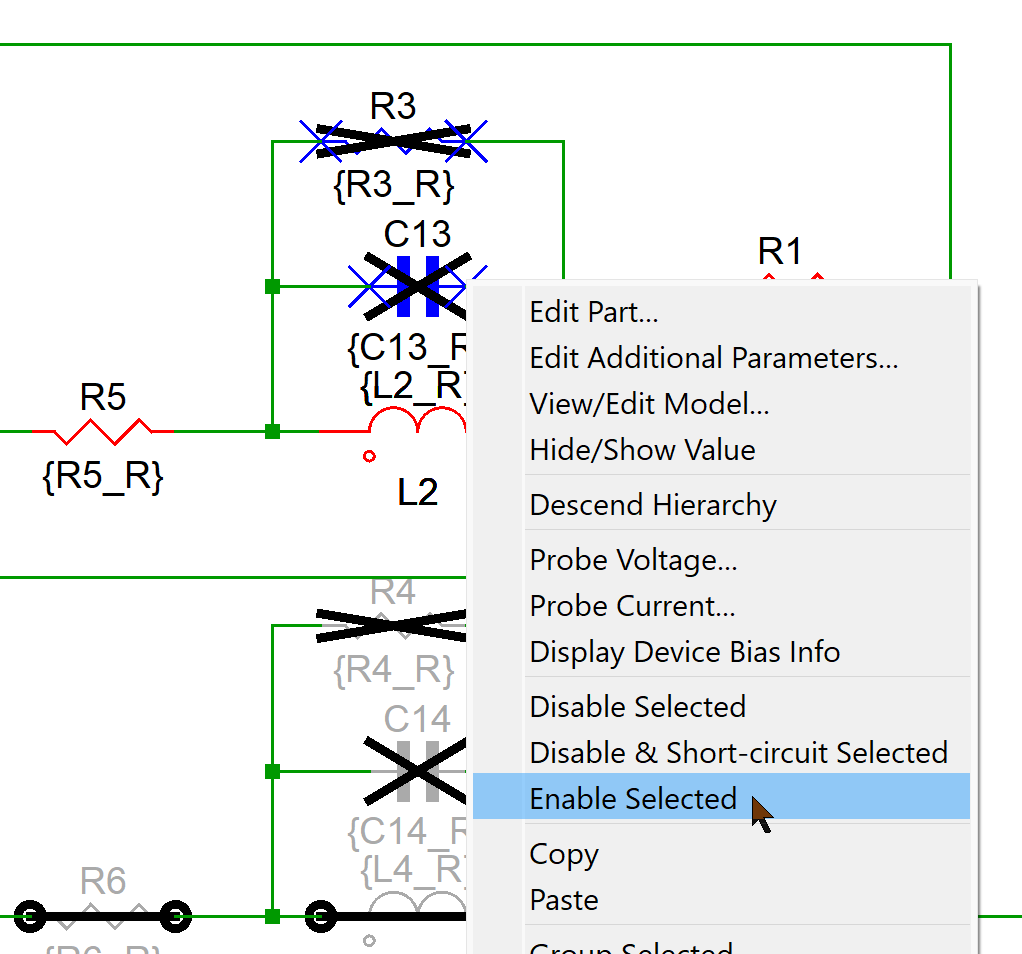

- Convert PDN Netlist to SIMPLIS and SIMetrix Compatible Netlists and Create Associated Symbol

- Using SIMetrix PDN test bench, characterize performance of Full PDN and R-Only PDN using worst-case expected load-transient current waveform

- Using SIMetrix testbench:

- Using SIMPLIS testbench with complete SIMPLIS converter model:

G.3 Extract Spice netlist of PDN from PCB layout

A variety of tools are available to extract a Spice model of the parasitic resistances, inductances and capacitances associated with the portions of a PCB layout connecting the output inductors of the power stage with the input terminals of the microprocessor load. These tools can take as input the physical layout of the PCB and then calculate the associated PCB parasitic impedances.

The details of this PCB parasitic extraction process differ from one tool to the next and are not the subject of this document. However, there are several items that these tools have in common. Many of these tools have their origins in the field of Signal Integrity. Many of them perform their analysis of the PCB layout in the frequency domain and have as a possible output a set of s-parameters. S-parameters are only defined in the frequency domain and as such are not applicable for the time-domain analyses required for predicting VRM output-voltage performance under extremely high di/dt load transitions. Fortunately, many of these tools have supplementary applications that will convert the S-parameter data to an equivalent Spice model made up of passive R, L and C components and controlled sources. During the conversion process, it is essential that the resulting networks exhibit passive network behavior. It is also important to submit these mathematically derived models to a causality check so that they do not exhibit nonphysical behavior.

When creating the Spice Model of the PDN, it is tempting to think that it is desirable to specify that the valid upper frequency range of the PDN model be as high as possible. Some tools will provide models that are valid up to 10 GHz or higher. However, from a practical perspective, less is often more. PDN models that are valid to frequencies up to 1 to 10 GHz can result in Spice models with more than 4000 to 6000 equivalent parasitic inductors and capacitors. A PDN with this many energy storage elements will result in impractically long simulation times.

Based on our experience, we recommend applying these constraints to the PDN extraction process.

- No more than 10 -12 ports

- No more than 100 poles (equivalent inductors and capacitors)

- Purely passive network behavior

- Passed a causality check

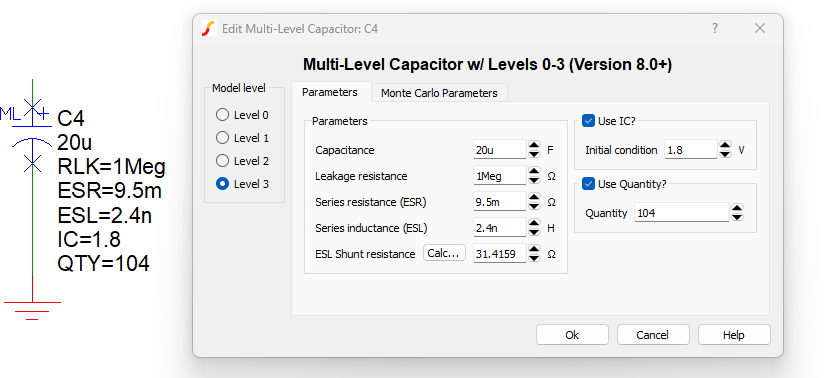

The PCB layout also defines the location of the bulk capacitors that are connected in parallel with the load. In order to minimize the number of ports of the PDN, it is important to group the capacitors into islands that reduce the number of ports of the PDN that connect to bulk capacitors to less than 6 or 7. For capacitors that occupy the same island of the PCB layout, it is important that all capacitors of the same type with the same values of C, ESR and ESL be grouped together in a single symbol using the Quantity feature as shown here.

The simulation speed is dramatically improved by using the Quantity feature rather than showing, in this example, 104 capacitors on the schematic in parallel. Bulk capacitors connected in parallel with the load via the PDN on different islands of the layout should be grouped with like capacitors on the same island.

Example of auto-generated PDN Spice model

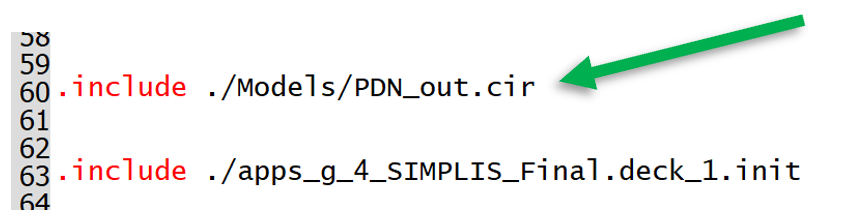

In this exercise, we will briefly examine the contents of the output of one of these PCB layout extraction routines that result in a Spice subcircuit model of the PDN shown in the schematic of Fig, G.1.

1. Open the file Models\PDN.cir in a text editor. You can observe the form and format of this Spice model of the PDN that we use in this study.

**********************************************************

** STATE-SPACE REALIZATION

** IN SPICE LANGUAGE

** This file is automatically generated

**********************************************************

** Created: 05-May-2021 by IdEM MP 12 (12.5.0)

**********************************************************

**

**********************************************************

** COMMENTS

**********************************************************

**

** Generated from: VR14_06A_MB_INT_10ohm_vsense_tie.spd

**

** VCCIN_Vsense::VCCIN

** VRTT::VCCIN

** Vph_N::PVCCIN_CPU0

** Vph_S::PVCCIN_CPU0

** North_VR_Caps::PVCCIN_CPU0

** South_VR_Caps::PVCCIN_CPU0

** Top_Cavity_Caps::PVCCIN_CPU0

** Btm_Cavity_Caps::PVCCIN_CPU0

** Btm_VR_Caps_N::PVCCIN_CPU0

** Btm_VR_Caps_S::PVCCIN_CPU0

**

** Sigrity Suite Version: 19.0.4.01041.258722 004

** Computer Host Name: FM6SRDS2035

**

** TouchstoneFormatFlag = 1

** GNDNET GND

** NETSLIST PVCCIN_CPU0, VCCIN

** Port 2 = PKGJ1-AA12 VCCIN

** Port 5 = BRDC1902-2 PVCCIN_CPU0

** Port 6 = BRDC1679-2 PVCCIN_CPU0

** Port 7 = BRDC1667-2 PVCCIN_CPU0

** Port 8 = BRDC1771-2 PVCCIN_CPU0

** Port 9 = BRDC1914-2 PVCCIN_CPU0

** Port 10 = BRDC1757-2 PVCCIN_CPU0

**

**

**********************************************************

**

**

**---------------------------

** Options Used in IdEM Flow

**---------------------------

**

** Fitting Options **

**

** Bandwidth: 5.0000e+08 Hz

** Order: [3 2 9]

** SplitType: none

** tol: 1.0000e-03

**

**---------------------------

**

** Passivity Options **

**

** Alg: SOC+HAM

** Max SOC it: 50

** Max HAM it: 50

** Freq sampling: manual

** In-band samples: 200

** Off-band samples: 100

** Optimization method: Model based

**

**---------------------------

**

** Netlist Options **

**

** Netlist format: SPICE standard

** Port reference: common

** Resistor synthesis: standard

**

**---------------------------

**

**************************************************************************

***{

***

*** The following was added by SIMPLIS Technologies, Inc. as a brief

*** description of a typical SPICE subcircuit file modeling a PDN

*** (Power Distribution Network) and how such a file can be converted

*** to be used by SIMPLIS in the SIMetrix/SIMPLIS environment.

***

***

*** This is an example SPICE subcircuit model for a 10-port PDN.

***

*** A SPICE subcircuit model for a PDN is typically generated by tools that

*** model the frequency-domain scattering characteristics of the

*** physical layout of the conductor/via of the printed circuit board,

*** with the possible inclusion of explicit capacitors and resistors

*** that are not parasitics.

***

*** Since SPICE usually works with node names and SIMPLIS works with node

*** numbers, SIMPLIS Technologies, Inc. has developed a PDN Parser

*** Tool to convert the SPICE subcircuit model into a subcircuit model

*** usable by SIMPLIS.

***

*** Another function of the PDN Parser Tool is to generate a SIMetrix /

*** SIMPLIS symbol for the PDN so that the symbol can be placed on a

*** schematic in SIMetrix/SIMPLIS to represent the PDN.

***

**************************************************************************

**************************************************************************

***

*** The following was added by SIMPLIS Technologies, Inc.

***

***

*** This is a file in SPICE format. If the first non white-space

*** character in a line is the asterisk (*), then this line is a

*** comment line. If the first character in a line is the plus

*** sign (+), then this line is a line of continuation.

***

*** Hence, the following three lines (without the three leading asterisks

*** and the tab character)

***

*** .subckt PDN_subckt a_1 a_2 a_3

*** + a_4 a_5 a_6

*** + a_7 a_8 a_9 a_10 ref

***

*** are equivalent to the following line (without the three leading

*** asterisks and the tab character)

***

*** .subckt PDN_subckt a_1 a_2 a_3 a_4 a_5 a_6 a_7 a_8 a_9 a_10 ref

***

**************************************************************************

**************************************************************************

***

*** NOTE from the particular tool generating this SPICE subcircuit file:

***

*** a_i --> input node associated to the port i

*** ref --> reference node, common for all the input nodes

***

***

*** The effective/example subcircuit line is:

***

*** .subckt PDN_subckt a_1 a_2 a_3 a_4 a_5 a_6 a_7 a_8 a_9 a_10 ref

***

***

*** The following was added by SIMPLIS Technologies, Inc.

***

***

*** Without any additional information, the PDN Parser Tool will create a

*** symbol with pin names of a_1, a_2, ..., ref.

***

*** If you edit the SPICE model file for the PDN and add additional

*** information, you can override the default pin names with more

*** meaningful pin names in the symbol.

***

*** The specification of desired pin names in your symbol are defined

*** through comment lines BEFORE the first .subckt line in this file.

*** Such a comment line must have at least four fields in the line,

*** where each field is a group of non white-space characters and the

*** fields are separated by one or more white-space characters. The

*** space character and the TAB character are considered white-space

*** characters.

***

*** FIELD #1

*** One ore more asterisk character(s) and this field MUST

*** start at the first column position in the line.

***

*** FIELD #2

*** The keyword SIMPLIS_PDN_PIN_NAME

***

*** FIELD #3

*** The node position in the .subckt line, with the first

*** node position denoted as position 1.

***

*** FIELD #4

*** The preferred pin name in the symbol for this node. It is

*** recommended that the pin names contain only alphanumeric

*** characters and the underscore (_) character. The first

*** character in a pin name should be an alphabet.

***

***

*** The following two example lines below, if the three leading asterisks

*** and the following tab characters were removed, will lead to a

*** symbol with a pin name of ABC for node a_1, and a pin name of DEF

*** for node a_3 for our example .subckt statement. As there were no

*** SIMPLIS_PDN_PIN_NAME statements defined for the other nodes on the

*** example .subckt line, the node names for these nodes will be used

*** as the pin names in the symbol.

***

*** Actual start of line

*** |

*** v

*** * SIMPLIS_PDN_PIN_NAME: 1 ABC

*** ****** SIMPLIS_PDN_PIN_NAME: 3 DEF

***

***

*** When this subcircuit file is fed into the SIMPLIS PDN Parser Tool as

*** the input file, the symbol created will have pin names of VOSENP,

*** VCCIN, Ph_N, Ph_S, Caps_1, Caps_2, Caps_3, Caps_4, Caps_5, Caps_6,

*** and ref because of the following 10 lines that contain the

*** SIMPLIS_PDN_PIN_NAME keyword:

***

***

*** SIMPLIS_PDN_PIN_NAME: 1 VOSENP

*** SIMPLIS_PDN_PIN_NAME: 2 VCCIN

*** SIMPLIS_PDN_PIN_NAME: 3 Ph_N

*** SIMPLIS_PDN_PIN_NAME: 4 Ph_S

*** SIMPLIS_PDN_PIN_NAME: 5 Caps_1

*** SIMPLIS_PDN_PIN_NAME: 6 Caps_2

*** SIMPLIS_PDN_PIN_NAME: 7 Caps_3

*** SIMPLIS_PDN_PIN_NAME: 8 Caps_4

*** SIMPLIS_PDN_PIN_NAME: 9 Caps_5

*** SIMPLIS_PDN_PIN_NAME: 10 Caps_6

***

***}

**************************************************************************

**********************************************************

* NOTE:

* a_i --> input node associated to the port i

* ref --> reference node, common for all the input nodes

**********************************************************

***********************************

* Interface (ports specification) *

***********************************

.subckt PDN_subckt

+ a_1 a_2 a_3 a_4 a_5 a_6 a_7 a_8 a_9 a_10 ref

***********************************

******************************************

* Main circuit connected to output nodes *

******************************************

* Port 1

VI_1 a_1 NI_1 0

RI_1 NI_1 ref 1.0000000000000000e+01

GC_1_1 ref NI_1 NS_1 0 -8.6267797685159894e-02

GC_1_2 ref NI_1 NS_2 0 -3.1695042667834995e-02

GC_1_3 ref NI_1 NS_3 0 8.9109795569324595e-06

GC_1_4 ref NI_1 NS_4 0 4.6362351844730615e-06

GC_1_5 ref NI_1 NS_5 0 -2.4338482544688482e-06

GC_1_6 ref NI_1 NS_6 0 4.8802468290969379e-07

GC_1_7 ref NI_1 NS_7 0 -1.1600208064491790e-06

GC_1_8 ref NI_1 NS_8 0 3.7847750692510811e-05

GC_1_9 ref NI_1 NS_9 0 -5.5735222338960090e-06

GC_1_10 ref NI_1 NS_10 0 -3.3098650194660351e-03

GC_1_11 ref NI_1 NS_11 0 4.9390447202489886e-04

GC_1_12 ref NI_1 NS_12 0 9.0147033246282097e-06

GC_1_13 ref NI_1 NS_13 0 8.1961743230962946e-06

GC_1_14 ref NI_1 NS_14 0 6.1765800840654062e-07

GC_1_15 ref NI_1 NS_15 0 7.2021614862563572e-07

GC_1_16 ref NI_1 NS_16 0 1.4229650136663458e-06

GC_1_17 ref NI_1 NS_17 0 3.7663889477511700e-05

GC_1_18 ref NI_1 NS_18 0 -1.1671942468833216e-06

GC_1_19 ref NI_1 NS_19 0 1.0494059227934194e-03

GC_1_20 ref NI_1 NS_20 0 1.0891550747099870e-04

GC_1_21 ref NI_1 NS_21 0 9.0172237810523149e-06

GC_1_22 ref NI_1 NS_22 0 -1.7756979378388187e-05

GC_1_23 ref NI_1 NS_23 0 2.9206105331601790e-06

GC_1_24 ref NI_1 NS_24 0 5.5178779040142569e-06

GC_1_25 ref NI_1 NS_25 0 1.4270540148621404e-07

GC_1_26 ref NI_1 NS_26 0 -1.4255587073852486e-06

GC_1_27 ref NI_1 NS_27 0 -1.7544975475673101e-08

GC_1_28 ref NI_1 NS_28 0 -1.3092249497200517e-02

GC_1_29 ref NI_1 NS_29 0 9.8520195076295882e-05

GC_1_30 ref NI_1 NS_30 0 9.0235673551378205e-06

GC_1_31 ref NI_1 NS_31 0 -9.8103360261359555e-06

GC_1_32 ref NI_1 NS_32 0 6.5740552102892825e-07

GC_1_33 ref NI_1 NS_33 0 -4.5673600819087673e-06

GC_1_34 ref NI_1 NS_34 0 -9.4657918506147485e-07

GC_1_35 ref NI_1 NS_35 0 7.7611323642627685e-06

GC_1_36 ref NI_1 NS_36 0 -8.9401257372897944e-07

GC_1_37 ref NI_1 NS_37 0 -1.9069202617826666e-03

GC_1_38 ref NI_1 NS_38 0 1.6582180944860601e-04

GC_1_39 ref NI_1 NS_39 0 9.0185703165906122e-06

GC_1_40 ref NI_1 NS_40 0 -1.8687812308921454e-05

GC_1_41 ref NI_1 NS_41 0 3.0744166141653231e-06

GC_1_42 ref NI_1 NS_42 0 5.5859351292285337e-06

GC_1_43 ref NI_1 NS_43 0 1.0999720688254255e-07

GC_1_44 ref NI_1 NS_44 0 5.3726852537005971e-06

GC_1_45 ref NI_1 NS_45 0 -3.2595331401758057e-07

GC_1_46 ref NI_1 NS_46 0 -1.2719714676119959e-02

GC_1_47 ref NI_1 NS_47 0 2.6914876912967898e-04

GC_1_48 ref NI_1 NS_48 0 9.0234390627329261e-06

GC_1_49 ref NI_1 NS_49 0 -7.0392242707099411e-06

GC_1_50 ref NI_1 NS_50 0 5.7018943734817043e-07

GC_1_51 ref NI_1 NS_51 0 -3.1674662614245012e-06

GC_1_52 ref NI_1 NS_52 0 -4.6496708419361174e-07

GC_1_53 ref NI_1 NS_53 0 1.7720071822318034e-05

GC_1_54 ref NI_1 NS_54 0 -1.1692744504199971e-06

GC_1_55 ref NI_1 NS_55 0 -6.1352610993221229e-04

GC_1_56 ref NI_1 NS_56 0 6.0707521227886231e-05

GC_1_57 ref NI_1 NS_57 0 9.0166123785306882e-06

GC_1_58 ref NI_1 NS_58 0 -1.1836456996217053e-07

GC_1_59 ref NI_1 NS_59 0 -3.5640678171593891e-08

GC_1_60 ref NI_1 NS_60 0 1.7632543924295680e-06

GC_1_61 ref NI_1 NS_61 0 2.1265937318331874e-07

GC_1_62 ref NI_1 NS_62 0 3.0628959093053036e-05

GC_1_63 ref NI_1 NS_63 0 -1.8480754892416378e-06

GC_1_64 ref NI_1 NS_64 0 -8.3328785078004748e-04

GC_1_65 ref NI_1 NS_65 0 9.7920179120612180e-05

GC_1_66 ref NI_1 NS_66 0 9.0166067328772064e-06

GC_1_67 ref NI_1 NS_67 0 -1.1972240605360346e-06

GC_1_68 ref NI_1 NS_68 0 1.1856682444338475e-07

GC_1_69 ref NI_1 NS_69 0 1.8810350983420390e-06

GC_1_70 ref NI_1 NS_70 0 2.1358983504161338e-07

GC_1_71 ref NI_1 NS_71 0 2.9598335832023110e-05

GC_1_72 ref NI_1 NS_72 0 -1.8202467305244511e-06

GC_1_73 ref NI_1 NS_73 0 -5.0302668975740908e-03

GC_1_74 ref NI_1 NS_74 0 2.2390301019291966e-04

GC_1_75 ref NI_1 NS_75 0 9.0198063392198828e-06

GC_1_76 ref NI_1 NS_76 0 -1.8742380972260078e-05

GC_1_77 ref NI_1 NS_77 0 2.9625665916699423e-06

GC_1_78 ref NI_1 NS_78 0 5.6139050859731395e-06

GC_1_79 ref NI_1 NS_79 0 7.3392732479095726e-08

GC_1_80 ref NI_1 NS_80 0 7.1672759455379924e-06

GC_1_81 ref NI_1 NS_81 0 -3.2161832621759689e-07

GC_1_82 ref NI_1 NS_82 0 -1.6061220581368239e-02

GC_1_83 ref NI_1 NS_83 0 2.5103826054070623e-04

GC_1_84 ref NI_1 NS_84 0 9.0258318610652617e-06

GC_1_85 ref NI_1 NS_85 0 -9.2864546088353147e-06

GC_1_86 ref NI_1 NS_86 0 4.6625219837504974e-07

GC_1_87 ref NI_1 NS_87 0 -3.3236262873932422e-06

GC_1_88 ref NI_1 NS_88 0 -6.2224219727727657e-07

GC_1_89 ref NI_1 NS_89 0 1.7356044019333759e-05

GC_1_90 ref NI_1 NS_90 0 -1.0579662627130972e-06

GD_1_1 ref NI_1 NA_1 0 6.2057089247737218e-01

GD_1_2 ref NI_1 NA_2 0 9.4073000096558241e-04

GD_1_3 ref NI_1 NA_3 0 -7.1507407511151484e-03

GD_1_4 ref NI_1 NA_4 0 5.5437299927774235e-02

GD_1_5 ref NI_1 NA_5 0 4.3237928004451979e-03

GD_1_6 ref NI_1 NA_6 0 4.8963781282800246e-02

GD_1_7 ref NI_1 NA_7 0 4.0652484331756223e-04

GD_1_8 ref NI_1 NA_8 0 4.0771928372521570e-04

GD_1_9 ref NI_1 NA_9 0 1.6615060594218776e-02

GD_1_10 ref NI_1 NA_10 0 6.4343757103560467e-02

*

* Port 2

VI_2 a_2 NI_2 0

RI_2 NI_2 ref 1.0000000000000000e+01

GC_2_1 ref NI_2 NS_1 0 -3.3098650194660680e-03

GC_2_2 ref NI_2 NS_2 0 4.9390447202490037e-04

GC_2_3 ref NI_2 NS_3 0 9.0147033246282114e-06

GC_2_4 ref NI_2 NS_4 0 8.1961743230962912e-06

GC_2_5 ref NI_2 NS_5 0 6.1765800840654020e-07

GC_2_6 ref NI_2 NS_6 0 7.2021614862563815e-07

GC_2_7 ref NI_2 NS_7 0 1.4229650136663443e-06

GC_2_8 ref NI_2 NS_8 0 3.7663889477511707e-05

GC_2_9 ref NI_2 NS_9 0 -1.1671942468833219e-06

GC_2_10 ref NI_2 NS_10 0 -9.1443571030223273e-03

GC_2_11 ref NI_2 NS_11 0 -4.0278181062021608e-04

GC_2_12 ref NI_2 NS_12 0 8.9857922465002056e-06

GC_2_13 ref NI_2 NS_13 0 8.6304262224935433e-06

GC_2_14 ref NI_2 NS_14 0 -4.0230609463657800e-07

GC_2_15 ref NI_2 NS_15 0 1.0146036759866554e-06

GC_2_16 ref NI_2 NS_16 0 -5.2985632962467365e-07

GC_2_17 ref NI_2 NS_17 0 3.8773974173881492e-05

GC_2_18 ref NI_2 NS_18 0 6.4247028747276582e-07

GC_2_19 ref NI_2 NS_19 0 -2.2065345067888912e-03

GC_2_20 ref NI_2 NS_20 0 -3.3557985960857592e-05

GC_2_21 ref NI_2 NS_21 0 9.0053729726399258e-06

GC_2_22 ref NI_2 NS_22 0 -1.8866392587987217e-05

GC_2_23 ref NI_2 NS_23 0 -8.5530294128342576e-07

GC_2_24 ref NI_2 NS_24 0 4.7319385239545600e-06

GC_2_25 ref NI_2 NS_25 0 3.6328674223072876e-07

GC_2_26 ref NI_2 NS_26 0 -1.2757545909645361e-06

GC_2_27 ref NI_2 NS_27 0 -4.1201547283237075e-07

GC_2_28 ref NI_2 NS_28 0 -1.6714798321519220e-02

GC_2_29 ref NI_2 NS_29 0 5.5753519317568721e-04

GC_2_30 ref NI_2 NS_30 0 9.0099210581159832e-06

GC_2_31 ref NI_2 NS_31 0 -1.0149466892259926e-05

GC_2_32 ref NI_2 NS_32 0 2.4297512171894839e-07

GC_2_33 ref NI_2 NS_33 0 -3.8706989579682522e-06

GC_2_34 ref NI_2 NS_34 0 -6.9071644142834058e-07

GC_2_35 ref NI_2 NS_35 0 7.6231888102927786e-06

GC_2_36 ref NI_2 NS_36 0 2.7188130785769556e-07

GC_2_37 ref NI_2 NS_37 0 -6.4223667118143146e-03

GC_2_38 ref NI_2 NS_38 0 1.1325885345753127e-04

GC_2_39 ref NI_2 NS_39 0 9.0061752846605501e-06

GC_2_40 ref NI_2 NS_40 0 -1.9874314394311989e-05

GC_2_41 ref NI_2 NS_41 0 -8.3811020978124109e-07

GC_2_42 ref NI_2 NS_42 0 4.7756778874707002e-06

GC_2_43 ref NI_2 NS_43 0 4.1089909537160262e-07

GC_2_44 ref NI_2 NS_44 0 5.5772304615432734e-06

GC_2_45 ref NI_2 NS_45 0 -1.1790975572598164e-07

GC_2_46 ref NI_2 NS_46 0 -1.3911213122728350e-02

GC_2_47 ref NI_2 NS_47 0 4.4197981775417574e-04

GC_2_48 ref NI_2 NS_48 0 9.0076104352446703e-06

GC_2_49 ref NI_2 NS_49 0 -7.3061839586875850e-06

GC_2_50 ref NI_2 NS_50 0 2.0876538998660666e-08

GC_2_51 ref NI_2 NS_51 0 -2.6678998222815130e-06

GC_2_52 ref NI_2 NS_52 0 -5.0202021112942395e-07

GC_2_53 ref NI_2 NS_53 0 1.7833281423929039e-05

GC_2_54 ref NI_2 NS_54 0 5.1825127612618784e-07

GC_2_55 ref NI_2 NS_55 0 -1.2201618426883704e-04

GC_2_56 ref NI_2 NS_56 0 -3.0145027242120960e-05

GC_2_57 ref NI_2 NS_57 0 9.0039833991268992e-06

GC_2_58 ref NI_2 NS_58 0 -1.6477350666071558e-07

GC_2_59 ref NI_2 NS_59 0 -6.6341233419396380e-07

GC_2_60 ref NI_2 NS_60 0 1.5022797165107343e-06

GC_2_61 ref NI_2 NS_61 0 1.8308691009460368e-08

GC_2_62 ref NI_2 NS_62 0 3.1146435976016691e-05

GC_2_63 ref NI_2 NS_63 0 4.4038250269697667e-07

GC_2_64 ref NI_2 NS_64 0 2.6217819915351091e-04

GC_2_65 ref NI_2 NS_65 0 6.1305915814840481e-06

GC_2_66 ref NI_2 NS_66 0 9.0045112555313580e-06

GC_2_67 ref NI_2 NS_67 0 -1.3000935170316406e-06

GC_2_68 ref NI_2 NS_68 0 -6.7420022972779699e-07

GC_2_69 ref NI_2 NS_69 0 1.5969279291525925e-06

GC_2_70 ref NI_2 NS_70 0 6.3140605369852125e-08

GC_2_71 ref NI_2 NS_71 0 3.0100767414671035e-05

GC_2_72 ref NI_2 NS_72 0 4.0059224890391213e-07

GC_2_73 ref NI_2 NS_73 0 -1.0808550191781847e-02

GC_2_74 ref NI_2 NS_74 0 2.2115128389801520e-04

GC_2_75 ref NI_2 NS_75 0 9.0049581092356858e-06

GC_2_76 ref NI_2 NS_76 0 -1.9890592830976056e-05

GC_2_77 ref NI_2 NS_77 0 -9.0872149630585791e-07

GC_2_78 ref NI_2 NS_78 0 4.7967578446840201e-06

GC_2_79 ref NI_2 NS_79 0 4.0432944218194290e-07

GC_2_80 ref NI_2 NS_80 0 7.3729627976287797e-06

GC_2_81 ref NI_2 NS_81 0 4.8324483084342229e-08

GC_2_82 ref NI_2 NS_82 0 -1.7520331460230732e-02

GC_2_83 ref NI_2 NS_83 0 4.6644592360619024e-04

GC_2_84 ref NI_2 NS_84 0 9.0054193807990271e-06

GC_2_85 ref NI_2 NS_85 0 -9.6162138566756280e-06

GC_2_86 ref NI_2 NS_86 0 -2.2666460113412741e-07

GC_2_87 ref NI_2 NS_87 0 -2.8281573294987830e-06

GC_2_88 ref NI_2 NS_88 0 -5.9007938645064709e-07

GC_2_89 ref NI_2 NS_89 0 1.7406179993585282e-05

GC_2_90 ref NI_2 NS_90 0 6.4175417379562041e-07

GD_2_1 ref NI_2 NA_1 0 9.4073000096567662e-04

GD_2_2 ref NI_2 NA_2 0 -5.8045203243176746e-01

GD_2_3 ref NI_2 NA_3 0 1.1012934791396646e-02

GD_2_4 ref NI_2 NA_4 0 5.9554804765230840e-02

GD_2_5 ref NI_2 NA_5 0 2.5796007360134942e-02

GD_2_6 ref NI_2 NA_6 0 5.0164962827198074e-02

GD_2_7 ref NI_2 NA_7 0 1.3849606921245586e-03

GD_2_8 ref NI_2 NA_8 0 -1.3192226213823248e-03

GD_2_9 ref NI_2 NA_9 0 4.2441749921709390e-02

GD_2_10 ref NI_2 NA_10 0 6.5635371833338285e-02

*

* Port 3

VI_3 a_3 NI_3 0

RI_3 NI_3 ref 1.0000000000000000e+01

GC_3_1 ref NI_3 NS_1 0 1.0494059227934129e-03

GC_3_2 ref NI_3 NS_2 0 1.0891550747099919e-04

GC_3_3 ref NI_3 NS_3 0 9.0172237810523149e-06

GC_3_4 ref NI_3 NS_4 0 -1.7756979378388187e-05

GC_3_5 ref NI_3 NS_5 0 2.9206105331601765e-06

GC_3_6 ref NI_3 NS_6 0 5.5178779040142543e-06

GC_3_7 ref NI_3 NS_7 0 1.4270540148621656e-07

GC_3_8 ref NI_3 NS_8 0 -1.4255587073852492e-06

GC_3_9 ref NI_3 NS_9 0 -1.7544975475672115e-08

GC_3_10 ref NI_3 NS_10 0 -2.2065345067889125e-03

GC_3_11 ref NI_3 NS_11 0 -3.3557985960857640e-05

GC_3_12 ref NI_3 NS_12 0 9.0053729726399258e-06

GC_3_13 ref NI_3 NS_13 0 -1.8866392587987200e-05

GC_3_14 ref NI_3 NS_14 0 -8.5530294128339040e-07

GC_3_15 ref NI_3 NS_15 0 4.7319385239545787e-06

GC_3_16 ref NI_3 NS_16 0 3.6328674223070886e-07

GC_3_17 ref NI_3 NS_17 0 -1.2757545909645259e-06

GC_3_18 ref NI_3 NS_18 0 -4.1201547283237916e-07

GC_3_19 ref NI_3 NS_19 0 -4.3543451992635207e-02

GC_3_20 ref NI_3 NS_20 0 -9.8828939859576365e-04

GC_3_21 ref NI_3 NS_21 0 8.9801747975822419e-06

GC_3_22 ref NI_3 NS_22 0 4.0704278975024792e-05

GC_3_23 ref NI_3 NS_23 0 1.6735639300139574e-06

GC_3_24 ref NI_3 NS_24 0 3.3673070396307742e-05

GC_3_25 ref NI_3 NS_25 0 1.8975627765101199e-07

GC_3_26 ref NI_3 NS_26 0 1.0330775463587333e-06

GC_3_27 ref NI_3 NS_27 0 -1.3673661981387673e-06

GC_3_28 ref NI_3 NS_28 0 -3.4776937212077901e-03

GC_3_29 ref NI_3 NS_29 0 1.2555738602249971e-04

GC_3_30 ref NI_3 NS_30 0 9.0157232927143767e-06

GC_3_31 ref NI_3 NS_31 0 2.3914140415663666e-05

GC_3_32 ref NI_3 NS_32 0 5.6265077650015187e-07

GC_3_33 ref NI_3 NS_33 0 -2.7982586369629624e-05

GC_3_34 ref NI_3 NS_34 0 -1.3171126419348591e-06

GC_3_35 ref NI_3 NS_35 0 5.2730374738329440e-08

GC_3_36 ref NI_3 NS_36 0 -6.9818028635982415e-07

GC_3_37 ref NI_3 NS_37 0 1.7034562663475521e-02

GC_3_38 ref NI_3 NS_38 0 -7.2345512627045787e-04

GC_3_39 ref NI_3 NS_39 0 8.9913003157722765e-06

GC_3_40 ref NI_3 NS_40 0 4.3076111940243213e-05

GC_3_41 ref NI_3 NS_41 0 1.9048905046994239e-06

GC_3_42 ref NI_3 NS_42 0 3.3856528458217794e-05

GC_3_43 ref NI_3 NS_43 0 2.4672057783982279e-07

GC_3_44 ref NI_3 NS_44 0 3.9894070527905772e-07

GC_3_45 ref NI_3 NS_45 0 -9.2522580519917488e-07

GC_3_46 ref NI_3 NS_46 0 -9.5415251455271844e-03

GC_3_47 ref NI_3 NS_47 0 3.8462591780560049e-04

GC_3_48 ref NI_3 NS_48 0 9.0165550653637313e-06

GC_3_49 ref NI_3 NS_49 0 1.7509334241665840e-05

GC_3_50 ref NI_3 NS_50 0 2.8915134240290087e-07

GC_3_51 ref NI_3 NS_51 0 -1.9437971587731361e-05

GC_3_52 ref NI_3 NS_52 0 -6.9409952770187027e-07

GC_3_53 ref NI_3 NS_53 0 -6.2573848111358059e-07

GC_3_54 ref NI_3 NS_54 0 -2.2653085063232666e-07

GC_3_55 ref NI_3 NS_55 0 6.6116542387365416e-03

GC_3_56 ref NI_3 NS_56 0 -5.6901123578366395e-05

GC_3_57 ref NI_3 NS_57 0 9.0060347570439581e-06

GC_3_58 ref NI_3 NS_58 0 -1.4418683705395469e-07

GC_3_59 ref NI_3 NS_59 0 3.1751908707567522e-07

GC_3_60 ref NI_3 NS_60 0 1.0067910808034622e-05

GC_3_61 ref NI_3 NS_61 0 2.9922307546074186e-07

GC_3_62 ref NI_3 NS_62 0 -9.7684118619394558e-07

GC_3_63 ref NI_3 NS_63 0 -3.8519549839380506e-07

GC_3_64 ref NI_3 NS_64 0 7.2615118140603452e-03

GC_3_65 ref NI_3 NS_65 0 -5.0210543662863665e-05

GC_3_66 ref NI_3 NS_66 0 9.0056956164157562e-06

GC_3_67 ref NI_3 NS_67 0 2.4211745584587793e-06

GC_3_68 ref NI_3 NS_68 0 4.7844295429191583e-07

GC_3_69 ref NI_3 NS_69 0 1.0803387283146924e-05

GC_3_70 ref NI_3 NS_70 0 3.0559821951673026e-07

GC_3_71 ref NI_3 NS_71 0 -9.3087561333641777e-07

GC_3_72 ref NI_3 NS_72 0 -3.8495585152809663e-07

GC_3_73 ref NI_3 NS_73 0 2.2571873715636522e-02

GC_3_74 ref NI_3 NS_74 0 -4.1898501197431724e-04

GC_3_75 ref NI_3 NS_75 0 8.9929582270792369e-06

GC_3_76 ref NI_3 NS_76 0 4.3377352610311509e-05

GC_3_77 ref NI_3 NS_77 0 2.0292595030045769e-06

GC_3_78 ref NI_3 NS_78 0 3.3910680940182101e-05

GC_3_79 ref NI_3 NS_79 0 3.6138895022276510e-07

GC_3_80 ref NI_3 NS_80 0 9.5068276684951191e-08

GC_3_81 ref NI_3 NS_81 0 -5.7073145020129118e-07

GC_3_82 ref NI_3 NS_82 0 -1.4846281996922917e-02

GC_3_83 ref NI_3 NS_83 0 6.4319465304124373e-04

GC_3_84 ref NI_3 NS_84 0 9.0213655232443903e-06

GC_3_85 ref NI_3 NS_85 0 2.2862339942658159e-05

GC_3_86 ref NI_3 NS_86 0 4.9837497684773326e-07

GC_3_87 ref NI_3 NS_87 0 -2.0400091302394984e-05

GC_3_88 ref NI_3 NS_88 0 -6.5071962141299452e-07

GC_3_89 ref NI_3 NS_89 0 -9.7276054362740445e-07

GC_3_90 ref NI_3 NS_90 0 2.6608758379812192e-07

GD_3_1 ref NI_3 NA_1 0 -7.1507407511151129e-03

GD_3_2 ref NI_3 NA_2 0 1.1012934791396721e-02

GD_3_3 ref NI_3 NA_3 0 -4.1076899123876709e-01

GD_3_4 ref NI_3 NA_4 0 1.2042281284224720e-02

GD_3_5 ref NI_3 NA_5 0 -5.5989674964219742e-02

GD_3_6 ref NI_3 NA_6 0 3.2147866251665783e-02

GD_3_7 ref NI_3 NA_7 0 -2.7688431280543060e-02

GD_3_8 ref NI_3 NA_8 0 -3.0762727937316187e-02

GD_3_9 ref NI_3 NA_9 0 -8.8950824702832693e-02

GD_3_10 ref NI_3 NA_10 0 4.8811779734872607e-02

*

* Port 4

VI_4 a_4 NI_4 0

RI_4 NI_4 ref 1.0000000000000000e+01

GC_4_1 ref NI_4 NS_1 0 -1.3092249497200554e-02

GC_4_2 ref NI_4 NS_2 0 9.8520195076297399e-05

GC_4_3 ref NI_4 NS_3 0 9.0235673551378205e-06

GC_4_4 ref NI_4 NS_4 0 -9.8103360261359572e-06

GC_4_5 ref NI_4 NS_5 0 6.5740552102893037e-07

GC_4_6 ref NI_4 NS_6 0 -4.5673600819087690e-06

GC_4_7 ref NI_4 NS_7 0 -9.4657918506147284e-07

GC_4_8 ref NI_4 NS_8 0 7.7611323642627668e-06

GC_4_9 ref NI_4 NS_9 0 -8.9401257372897933e-07

GC_4_10 ref NI_4 NS_10 0 -1.6714798321519255e-02

GC_4_11 ref NI_4 NS_11 0 5.5753519317568677e-04

GC_4_12 ref NI_4 NS_12 0 9.0099210581159832e-06

GC_4_13 ref NI_4 NS_13 0 -1.0149466892259918e-05

GC_4_14 ref NI_4 NS_14 0 2.4297512171888963e-07

GC_4_15 ref NI_4 NS_15 0 -3.8706989579682370e-06

GC_4_16 ref NI_4 NS_16 0 -6.9071644142836334e-07

GC_4_17 ref NI_4 NS_17 0 7.6231888102927845e-06

GC_4_18 ref NI_4 NS_18 0 2.7188130785768529e-07

GC_4_19 ref NI_4 NS_19 0 -3.4776937212077602e-03

GC_4_20 ref NI_4 NS_20 0 1.2555738602249862e-04

GC_4_21 ref NI_4 NS_21 0 9.0157232927143733e-06

GC_4_22 ref NI_4 NS_22 0 2.3914140415663677e-05

GC_4_23 ref NI_4 NS_23 0 5.6265077650015017e-07

GC_4_24 ref NI_4 NS_24 0 -2.7982586369629624e-05

GC_4_25 ref NI_4 NS_25 0 -1.3171126419348714e-06

GC_4_26 ref NI_4 NS_26 0 5.2730374738327045e-08

GC_4_27 ref NI_4 NS_27 0 -6.9818028635982394e-07

GC_4_28 ref NI_4 NS_28 0 -2.5934450401041448e-02

GC_4_29 ref NI_4 NS_29 0 -1.8209570863374214e-03

GC_4_30 ref NI_4 NS_30 0 8.9976453393100652e-06

GC_4_31 ref NI_4 NS_31 0 1.1194879271914931e-05

GC_4_32 ref NI_4 NS_32 0 -1.3989268520274667e-07

GC_4_33 ref NI_4 NS_33 0 2.2592033323705781e-05

GC_4_34 ref NI_4 NS_34 0 1.4655389645701242e-06

GC_4_35 ref NI_4 NS_35 0 1.5806042176860678e-06

GC_4_36 ref NI_4 NS_36 0 -2.4093829183233151e-07

GC_4_37 ref NI_4 NS_37 0 -1.4526875495294295e-04

GC_4_38 ref NI_4 NS_38 0 4.7830620367652832e-05

GC_4_39 ref NI_4 NS_39 0 9.0179858100972045e-06

GC_4_40 ref NI_4 NS_40 0 2.5168732609527666e-05

GC_4_41 ref NI_4 NS_41 0 5.3910289571713692e-07

GC_4_42 ref NI_4 NS_42 0 -2.8206194858527775e-05

GC_4_43 ref NI_4 NS_43 0 -1.1505303033374653e-06

GC_4_44 ref NI_4 NS_44 0 1.2640543693633516e-06

GC_4_45 ref NI_4 NS_45 0 -5.1802673995171814e-07

GC_4_46 ref NI_4 NS_46 0 6.8860540724011085e-03

GC_4_47 ref NI_4 NS_47 0 -8.0053587785672796e-04

GC_4_48 ref NI_4 NS_48 0 9.0061775211330015e-06

GC_4_49 ref NI_4 NS_49 0 8.3725645706786328e-06

GC_4_50 ref NI_4 NS_50 0 -1.0191164244283731e-07

GC_4_51 ref NI_4 NS_51 0 1.5805333764112172e-05

GC_4_52 ref NI_4 NS_52 0 9.5828834450392623e-07

GC_4_53 ref NI_4 NS_53 0 3.4581923998000089e-06

GC_4_54 ref NI_4 NS_54 0 5.1268033063688493e-08

GC_4_55 ref NI_4 NS_55 0 -1.0786750556904368e-02

GC_4_56 ref NI_4 NS_56 0 3.6285373880600753e-04

GC_4_57 ref NI_4 NS_57 0 9.0130994400621619e-06

GC_4_58 ref NI_4 NS_58 0 4.1789336610014208e-07

GC_4_59 ref NI_4 NS_59 0 4.2404267850232855e-07

GC_4_60 ref NI_4 NS_60 0 -8.3403936866102228e-06

GC_4_61 ref NI_4 NS_61 0 -7.0954330483442254e-07

GC_4_62 ref NI_4 NS_62 0 6.1862373865910469e-06

GC_4_63 ref NI_4 NS_63 0 3.9037319810983195e-09

GC_4_64 ref NI_4 NS_64 0 -9.7405602613881339e-03

GC_4_65 ref NI_4 NS_65 0 3.3738448096730443e-04

GC_4_66 ref NI_4 NS_66 0 9.0134172030788365e-06

GC_4_67 ref NI_4 NS_67 0 1.8572138827498765e-06

GC_4_68 ref NI_4 NS_68 0 4.7616997890104674e-07

GC_4_69 ref NI_4 NS_69 0 -8.9533501352535938e-06

GC_4_70 ref NI_4 NS_70 0 -7.1006594851413536e-07

GC_4_71 ref NI_4 NS_71 0 5.9793469596960708e-06

GC_4_72 ref NI_4 NS_72 0 -1.8547544166567148e-08

GC_4_73 ref NI_4 NS_73 0 2.1931882924623235e-03

GC_4_74 ref NI_4 NS_74 0 -3.8718520063722567e-05

GC_4_75 ref NI_4 NS_75 0 9.0192242042872578e-06

GC_4_76 ref NI_4 NS_76 0 2.5161891876443333e-05

GC_4_77 ref NI_4 NS_77 0 6.3123338673149720e-07

GC_4_78 ref NI_4 NS_78 0 -2.8229643808002403e-05

GC_4_79 ref NI_4 NS_79 0 -1.1034939228437410e-06

GC_4_80 ref NI_4 NS_80 0 1.5095149560273771e-06

GC_4_81 ref NI_4 NS_81 0 -4.1178066131937395e-07

GC_4_82 ref NI_4 NS_82 0 4.0318179619227158e-04

GC_4_83 ref NI_4 NS_83 0 -1.0064266561275365e-04

GC_4_84 ref NI_4 NS_84 0 9.0046303639161579e-06

GC_4_85 ref NI_4 NS_85 0 1.1655623652954365e-05

GC_4_86 ref NI_4 NS_86 0 -5.1581920447100495e-07

GC_4_87 ref NI_4 NS_87 0 1.6917326089045507e-05

GC_4_88 ref NI_4 NS_88 0 1.1245452442394209e-06

GC_4_89 ref NI_4 NS_89 0 3.2905726603533637e-06

GC_4_90 ref NI_4 NS_90 0 3.2135702612771534e-07

GD_4_1 ref NI_4 NA_1 0 5.5437299927774353e-02

GD_4_2 ref NI_4 NA_2 0 5.9554804765230999e-02

GD_4_3 ref NI_4 NA_3 0 1.2042281284224644e-02

GD_4_4 ref NI_4 NA_4 0 -4.6634707500615025e-01

GD_4_5 ref NI_4 NA_5 0 -6.9028055489575124e-04

GD_4_6 ref NI_4 NA_6 0 -8.4682848726227947e-03

GD_4_7 ref NI_4 NA_7 0 3.8337132136777821e-02

GD_4_8 ref NI_4 NA_8 0 3.4362172378454334e-02

GD_4_9 ref NI_4 NA_9 0 -8.7325356282884591e-03

GD_4_10 ref NI_4 NA_10 0 1.3353194813904362e-03

*

* Port 5

VI_5 a_5 NI_5 0

RI_5 NI_5 ref 1.0000000000000000e+01

GC_5_1 ref NI_5 NS_1 0 -1.9069202617826755e-03

GC_5_2 ref NI_5 NS_2 0 1.6582180944860607e-04

GC_5_3 ref NI_5 NS_3 0 9.0185703165906122e-06

GC_5_4 ref NI_5 NS_4 0 -1.8687812308921454e-05

GC_5_5 ref NI_5 NS_5 0 3.0744166141653252e-06

GC_5_6 ref NI_5 NS_6 0 5.5859351292285346e-06

GC_5_7 ref NI_5 NS_7 0 1.0999720688254228e-07

GC_5_8 ref NI_5 NS_8 0 5.3726852537005962e-06

GC_5_9 ref NI_5 NS_9 0 -3.2595331401758073e-07

GC_5_10 ref NI_5 NS_10 0 -6.4223667118143831e-03

GC_5_11 ref NI_5 NS_11 0 1.1325885345753319e-04

GC_5_12 ref NI_5 NS_12 0 9.0061752846605501e-06

GC_5_13 ref NI_5 NS_13 0 -1.9874314394311986e-05

GC_5_14 ref NI_5 NS_14 0 -8.3811020978125633e-07

GC_5_15 ref NI_5 NS_15 0 4.7756778874706918e-06

GC_5_16 ref NI_5 NS_16 0 4.1089909537160284e-07

GC_5_17 ref NI_5 NS_17 0 5.5772304615432725e-06

GC_5_18 ref NI_5 NS_18 0 -1.1790975572598072e-07

GC_5_19 ref NI_5 NS_19 0 1.7034562663475639e-02

GC_5_20 ref NI_5 NS_20 0 -7.2345512627046069e-04

GC_5_21 ref NI_5 NS_21 0 8.9913003157722782e-06

GC_5_22 ref NI_5 NS_22 0 4.3076111940243193e-05

GC_5_23 ref NI_5 NS_23 0 1.9048905046994265e-06

GC_5_24 ref NI_5 NS_24 0 3.3856528458217801e-05

GC_5_25 ref NI_5 NS_25 0 2.4672057783981867e-07

GC_5_26 ref NI_5 NS_26 0 3.9894070527905777e-07

GC_5_27 ref NI_5 NS_27 0 -9.2522580519917330e-07

GC_5_28 ref NI_5 NS_28 0 -1.4526875495291986e-04

GC_5_29 ref NI_5 NS_29 0 4.7830620367653577e-05

GC_5_30 ref NI_5 NS_30 0 9.0179858100972045e-06

GC_5_31 ref NI_5 NS_31 0 2.5168732609527663e-05

GC_5_32 ref NI_5 NS_32 0 5.3910289571713300e-07

GC_5_33 ref NI_5 NS_33 0 -2.8206194858527796e-05

GC_5_34 ref NI_5 NS_34 0 -1.1505303033374498e-06

GC_5_35 ref NI_5 NS_35 0 1.2640543693633524e-06

GC_5_36 ref NI_5 NS_36 0 -5.1802673995171560e-07

GC_5_37 ref NI_5 NS_37 0 -4.0305770664744903e-02

GC_5_38 ref NI_5 NS_38 0 -1.1370969029371408e-03

GC_5_39 ref NI_5 NS_39 0 8.9866194570585175e-06

GC_5_40 ref NI_5 NS_40 0 4.5177540290490744e-05

GC_5_41 ref NI_5 NS_41 0 2.3470209813999972e-06

GC_5_42 ref NI_5 NS_42 0 3.3911784685075253e-05

GC_5_43 ref NI_5 NS_43 0 1.2454431461380759e-07

GC_5_44 ref NI_5 NS_44 0 1.1760896885767779e-06

GC_5_45 ref NI_5 NS_45 0 -6.7476369611855529e-07

GC_5_46 ref NI_5 NS_46 0 -1.2932967558326984e-02

GC_5_47 ref NI_5 NS_47 0 5.2441127612929664e-04

GC_5_48 ref NI_5 NS_48 0 9.0169497588870285e-06

GC_5_49 ref NI_5 NS_49 0 1.8535546625059047e-05

GC_5_50 ref NI_5 NS_50 0 3.7844920535875493e-08

GC_5_51 ref NI_5 NS_51 0 -1.9506460905956998e-05

GC_5_52 ref NI_5 NS_52 0 -5.8786220313476392e-07

GC_5_53 ref NI_5 NS_53 0 2.5539354991338167e-06

GC_5_54 ref NI_5 NS_54 0 -8.4259578336112169e-08

GC_5_55 ref NI_5 NS_55 0 3.0731981119458320e-03

GC_5_56 ref NI_5 NS_56 0 -1.6865336622807139e-04

GC_5_57 ref NI_5 NS_57 0 9.0067969850091516e-06

GC_5_58 ref NI_5 NS_58 0 -2.3626949621456897e-07

GC_5_59 ref NI_5 NS_59 0 6.3078992251021372e-07

GC_5_60 ref NI_5 NS_60 0 1.0051430455082109e-05

GC_5_61 ref NI_5 NS_61 0 3.1460935294264514e-07

GC_5_62 ref NI_5 NS_62 0 4.5076106096994625e-06

GC_5_63 ref NI_5 NS_63 0 -2.0814380453973330e-07

GC_5_64 ref NI_5 NS_64 0 3.7757459912144222e-03

GC_5_65 ref NI_5 NS_65 0 -1.9431943364829512e-04

GC_5_66 ref NI_5 NS_66 0 9.0065101448898509e-06

GC_5_67 ref NI_5 NS_67 0 2.4500748927323490e-06

GC_5_68 ref NI_5 NS_68 0 8.2563474868312438e-07

GC_5_69 ref NI_5 NS_69 0 1.0776774189346398e-05

GC_5_70 ref NI_5 NS_70 0 3.1600549760124676e-07

GC_5_71 ref NI_5 NS_71 0 4.3616727885520021e-06

GC_5_72 ref NI_5 NS_72 0 -2.2084847783170817e-07

GC_5_73 ref NI_5 NS_73 0 2.0741788398399044e-02

GC_5_74 ref NI_5 NS_74 0 -1.0526219675052013e-03

GC_5_75 ref NI_5 NS_75 0 8.9940481511069325e-06

GC_5_76 ref NI_5 NS_76 0 4.5359743165954981e-05

GC_5_77 ref NI_5 NS_77 0 2.6923209303201161e-06

GC_5_78 ref NI_5 NS_78 0 3.3851062797887209e-05

GC_5_79 ref NI_5 NS_79 0 2.3298284685613886e-07

GC_5_80 ref NI_5 NS_80 0 1.2341213804704578e-06

GC_5_81 ref NI_5 NS_81 0 -4.3519147750590629e-07

GC_5_82 ref NI_5 NS_82 0 -2.3873930621022107e-02

GC_5_83 ref NI_5 NS_83 0 9.6329391202184123e-04

GC_5_84 ref NI_5 NS_84 0 9.0196298954355695e-06

GC_5_85 ref NI_5 NS_85 0 2.4269407857979663e-05

GC_5_86 ref NI_5 NS_86 0 -8.3295863920132870e-08

GC_5_87 ref NI_5 NS_87 0 -2.0399445185749023e-05

GC_5_88 ref NI_5 NS_88 0 -5.9799080578712022e-07

GC_5_89 ref NI_5 NS_89 0 2.2909870623594059e-06

GC_5_90 ref NI_5 NS_90 0 3.2668031266109363e-07

GD_5_1 ref NI_5 NA_1 0 4.3237928004452430e-03

GD_5_2 ref NI_5 NA_2 0 2.5796007360135188e-02

GD_5_3 ref NI_5 NA_3 0 -5.5989674964220193e-02

GD_5_4 ref NI_5 NA_4 0 -6.9028055489588156e-04

GD_5_5 ref NI_5 NA_5 0 -4.2103474608866082e-01

GD_5_6 ref NI_5 NA_6 0 4.3423671041051944e-02

GD_5_7 ref NI_5 NA_7 0 -8.8280354409099732e-03

GD_5_8 ref NI_5 NA_8 0 -1.1249709020995006e-02

GD_5_9 ref NI_5 NA_9 0 -6.3365427706893462e-02

GD_5_10 ref NI_5 NA_10 0 8.0261604927659588e-02

*

* Port 6

VI_6 a_6 NI_6 0

RI_6 NI_6 ref 1.0000000000000000e+01

GC_6_1 ref NI_6 NS_1 0 -1.2719714676119967e-02

GC_6_2 ref NI_6 NS_2 0 2.6914876912967898e-04

GC_6_3 ref NI_6 NS_3 0 9.0234390627329227e-06

GC_6_4 ref NI_6 NS_4 0 -7.0392242707099394e-06

GC_6_5 ref NI_6 NS_5 0 5.7018943734816947e-07

GC_6_6 ref NI_6 NS_6 0 -3.1674662614244966e-06

GC_6_7 ref NI_6 NS_7 0 -4.6496708419361571e-07

GC_6_8 ref NI_6 NS_8 0 1.7720071822318034e-05

GC_6_9 ref NI_6 NS_9 0 -1.1692744504199986e-06

GC_6_10 ref NI_6 NS_10 0 -1.3911213122728491e-02

GC_6_11 ref NI_6 NS_11 0 4.4197981775418019e-04

GC_6_12 ref NI_6 NS_12 0 9.0076104352446754e-06

GC_6_13 ref NI_6 NS_13 0 -7.3061839586875926e-06

GC_6_14 ref NI_6 NS_14 0 2.0876538998671933e-08

GC_6_15 ref NI_6 NS_15 0 -2.6678998222815367e-06

GC_6_16 ref NI_6 NS_16 0 -5.0202021112940606e-07

GC_6_17 ref NI_6 NS_17 0 1.7833281423929028e-05

GC_6_18 ref NI_6 NS_18 0 5.1825127612619292e-07

GC_6_19 ref NI_6 NS_19 0 -9.5415251455274984e-03

GC_6_20 ref NI_6 NS_20 0 3.8462591780560651e-04

GC_6_21 ref NI_6 NS_21 0 9.0165550653637381e-06

GC_6_22 ref NI_6 NS_22 0 1.7509334241665840e-05

GC_6_23 ref NI_6 NS_23 0 2.8915134240290267e-07

GC_6_24 ref NI_6 NS_24 0 -1.9437971587731361e-05

GC_6_25 ref NI_6 NS_25 0 -6.9409952770186837e-07

GC_6_26 ref NI_6 NS_26 0 -6.2573848111358006e-07

GC_6_27 ref NI_6 NS_27 0 -2.2653085063232488e-07

GC_6_28 ref NI_6 NS_28 0 6.8860540724009125e-03

GC_6_29 ref NI_6 NS_29 0 -8.0053587785672211e-04

GC_6_30 ref NI_6 NS_30 0 9.0061775211329981e-06

GC_6_31 ref NI_6 NS_31 0 8.3725645706786328e-06

GC_6_32 ref NI_6 NS_32 0 -1.0191164244283252e-07

GC_6_33 ref NI_6 NS_33 0 1.5805333764112185e-05

GC_6_34 ref NI_6 NS_34 0 9.5828834450393639e-07

GC_6_35 ref NI_6 NS_35 0 3.4581923998000102e-06

GC_6_36 ref NI_6 NS_36 0 5.1268033063690168e-08

GC_6_37 ref NI_6 NS_37 0 -1.2932967558327083e-02

GC_6_38 ref NI_6 NS_38 0 5.2441127612929826e-04

GC_6_39 ref NI_6 NS_39 0 9.0169497588870251e-06

GC_6_40 ref NI_6 NS_40 0 1.8535546625059041e-05

GC_6_41 ref NI_6 NS_41 0 3.7844920535875705e-08

GC_6_42 ref NI_6 NS_42 0 -1.9506460905956998e-05

GC_6_43 ref NI_6 NS_43 0 -5.8786220313476296e-07

GC_6_44 ref NI_6 NS_44 0 2.5539354991338167e-06

GC_6_45 ref NI_6 NS_45 0 -8.4259578336112261e-08

GC_6_46 ref NI_6 NS_46 0 -6.9826550723102190e-02

GC_6_47 ref NI_6 NS_47 0 -7.3238113361288675e-04

GC_6_48 ref NI_6 NS_48 0 8.9980021606135215e-06

GC_6_49 ref NI_6 NS_49 0 5.9429376255094809e-06

GC_6_50 ref NI_6 NS_50 0 1.6695184349408163e-07

GC_6_51 ref NI_6 NS_51 0 1.0964641041084742e-05

GC_6_52 ref NI_6 NS_52 0 5.0886639225722651e-07

GC_6_53 ref NI_6 NS_53 0 8.2204290768648394e-06

GC_6_54 ref NI_6 NS_54 0 1.6243162316999757e-07

GC_6_55 ref NI_6 NS_55 0 -1.4482499912375438e-02

GC_6_56 ref NI_6 NS_56 0 4.3675175148265782e-04

GC_6_57 ref NI_6 NS_57 0 9.0121965945465362e-06

GC_6_58 ref NI_6 NS_58 0 3.7553346259652109e-07

GC_6_59 ref NI_6 NS_59 0 1.7039763936429588e-07

GC_6_60 ref NI_6 NS_60 0 -5.7728592262244378e-06

GC_6_61 ref NI_6 NS_61 0 -4.1385785236984287e-07

GC_6_62 ref NI_6 NS_62 0 1.4384860116162887e-05

GC_6_63 ref NI_6 NS_63 0 2.3480676190349381e-07

GC_6_64 ref NI_6 NS_64 0 -1.4236559521248996e-02

GC_6_65 ref NI_6 NS_65 0 4.3083533860830878e-04

GC_6_66 ref NI_6 NS_66 0 9.0125014995673962e-06

GC_6_67 ref NI_6 NS_67 0 1.4265135194478007e-06

GC_6_68 ref NI_6 NS_68 0 2.1539325635599773e-07

GC_6_69 ref NI_6 NS_69 0 -6.1989416280953139e-06

GC_6_70 ref NI_6 NS_70 0 -4.0507089270896474e-07

GC_6_71 ref NI_6 NS_71 0 1.3900087141622022e-05

GC_6_72 ref NI_6 NS_72 0 2.0788666732169318e-07

GC_6_73 ref NI_6 NS_73 0 -1.3925280502172201e-02

GC_6_74 ref NI_6 NS_74 0 5.4550706141284213e-04

GC_6_75 ref NI_6 NS_75 0 9.0169493465309305e-06

GC_6_76 ref NI_6 NS_76 0 1.8575919234558075e-05

GC_6_77 ref NI_6 NS_77 0 -4.1555089519204663e-08

GC_6_78 ref NI_6 NS_78 0 -1.9489365244197635e-05

GC_6_79 ref NI_6 NS_79 0 -5.7581258501875995e-07

GC_6_80 ref NI_6 NS_80 0 3.3835481488918338e-06

GC_6_81 ref NI_6 NS_81 0 -1.3547580006848630e-08

GC_6_82 ref NI_6 NS_82 0 -7.0641256326003992e-03

GC_6_83 ref NI_6 NS_83 0 -5.0072181086261661e-04

GC_6_84 ref NI_6 NS_84 0 9.0033294948750455e-06

GC_6_85 ref NI_6 NS_85 0 8.1441773734862044e-06

GC_6_86 ref NI_6 NS_86 0 2.4714140064430686e-07

GC_6_87 ref NI_6 NS_87 0 1.1610745752638747e-05

GC_6_88 ref NI_6 NS_88 0 6.1476632416056118e-07

GC_6_89 ref NI_6 NS_89 0 7.9970297618602091e-06

GC_6_90 ref NI_6 NS_90 0 2.4497830741259585e-07

GD_6_1 ref NI_6 NA_1 0 4.8963781282800274e-02

GD_6_2 ref NI_6 NA_2 0 5.0164962827198512e-02

GD_6_3 ref NI_6 NA_3 0 3.2147866251666914e-02

GD_6_4 ref NI_6 NA_4 0 -8.4682848726220540e-03

GD_6_5 ref NI_6 NA_5 0 4.3423671041052402e-02

GD_6_6 ref NI_6 NA_6 0 -3.0030976857356367e-01

GD_6_7 ref NI_6 NA_7 0 5.2778514611757400e-02

GD_6_8 ref NI_6 NA_8 0 5.1842726999448981e-02

GD_6_9 ref NI_6 NA_9 0 4.7273353442177826e-02

GD_6_10 ref NI_6 NA_10 0 4.5621929783173192e-02

*

* Port 7

VI_7 a_7 NI_7 0

RI_7 NI_7 ref 1.0000000000000000e+01

GC_7_1 ref NI_7 NS_1 0 -6.1352610993222314e-04

GC_7_2 ref NI_7 NS_2 0 6.0707521227887972e-05

GC_7_3 ref NI_7 NS_3 0 9.0166123785306882e-06

GC_7_4 ref NI_7 NS_4 0 -1.1836456996215605e-07

GC_7_5 ref NI_7 NS_5 0 -3.5640678171606696e-08

GC_7_6 ref NI_7 NS_6 0 1.7632543924295688e-06

GC_7_7 ref NI_7 NS_7 0 2.1265937318331786e-07

GC_7_8 ref NI_7 NS_8 0 3.0628959093053036e-05

GC_7_9 ref NI_7 NS_9 0 -1.8480754892416376e-06

GC_7_10 ref NI_7 NS_10 0 -1.2201618426892783e-04

GC_7_11 ref NI_7 NS_11 0 -3.0145027242119334e-05

GC_7_12 ref NI_7 NS_12 0 9.0039833991269043e-06

GC_7_13 ref NI_7 NS_13 0 -1.6477350666077921e-07

GC_7_14 ref NI_7 NS_14 0 -6.6341233419393130e-07

GC_7_15 ref NI_7 NS_15 0 1.5022797165107307e-06

GC_7_16 ref NI_7 NS_16 0 1.8308691009458360e-08

GC_7_17 ref NI_7 NS_17 0 3.1146435976016685e-05

GC_7_18 ref NI_7 NS_18 0 4.4038250269698371e-07

GC_7_19 ref NI_7 NS_19 0 6.6116542387365329e-03

GC_7_20 ref NI_7 NS_20 0 -5.6901123578366727e-05

GC_7_21 ref NI_7 NS_21 0 9.0060347570439581e-06

GC_7_22 ref NI_7 NS_22 0 -1.4418683705395000e-07

GC_7_23 ref NI_7 NS_23 0 3.1751908707570550e-07

GC_7_24 ref NI_7 NS_24 0 1.0067910808034632e-05

GC_7_25 ref NI_7 NS_25 0 2.9922307546072445e-07

GC_7_26 ref NI_7 NS_26 0 -9.7684118619395849e-07

GC_7_27 ref NI_7 NS_27 0 -3.8519549839380050e-07

GC_7_28 ref NI_7 NS_28 0 -1.0786750556904527e-02

GC_7_29 ref NI_7 NS_29 0 3.6285373880601274e-04

GC_7_30 ref NI_7 NS_30 0 9.0130994400621636e-06

GC_7_31 ref NI_7 NS_31 0 4.1789336610013414e-07

GC_7_32 ref NI_7 NS_32 0 4.2404267850229314e-07

GC_7_33 ref NI_7 NS_33 0 -8.3403936866102178e-06

GC_7_34 ref NI_7 NS_34 0 -7.0954330483443270e-07

GC_7_35 ref NI_7 NS_35 0 6.1862373865910334e-06

GC_7_36 ref NI_7 NS_36 0 3.9037319811070024e-09

GC_7_37 ref NI_7 NS_37 0 3.0731981119457800e-03

GC_7_38 ref NI_7 NS_38 0 -1.6865336622807074e-04

GC_7_39 ref NI_7 NS_39 0 9.0067969850091482e-06

GC_7_40 ref NI_7 NS_40 0 -2.3626949621457807e-07

GC_7_41 ref NI_7 NS_41 0 6.3078992251020694e-07

GC_7_42 ref NI_7 NS_42 0 1.0051430455082100e-05

GC_7_43 ref NI_7 NS_43 0 3.1460935294264191e-07

GC_7_44 ref NI_7 NS_44 0 4.5076106096994608e-06

GC_7_45 ref NI_7 NS_45 0 -2.0814380453973142e-07

GC_7_46 ref NI_7 NS_46 0 -1.4482499912375430e-02

GC_7_47 ref NI_7 NS_47 0 4.3675175148265701e-04

GC_7_48 ref NI_7 NS_48 0 9.0121965945465362e-06

GC_7_49 ref NI_7 NS_49 0 3.7553346259651516e-07

GC_7_50 ref NI_7 NS_50 0 1.7039763936430345e-07

GC_7_51 ref NI_7 NS_51 0 -5.7728592262244488e-06

GC_7_52 ref NI_7 NS_52 0 -4.1385785236983795e-07

GC_7_53 ref NI_7 NS_53 0 1.4384860116162883e-05

GC_7_54 ref NI_7 NS_54 0 2.3480676190349595e-07

GC_7_55 ref NI_7 NS_55 0 -5.4721577193795799e-02

GC_7_56 ref NI_7 NS_56 0 -4.4841704656062639e-04

GC_7_57 ref NI_7 NS_57 0 9.0014484351026099e-06

GC_7_58 ref NI_7 NS_58 0 -5.0011919258339854e-07

GC_7_59 ref NI_7 NS_59 0 3.2093160856361552e-07

GC_7_60 ref NI_7 NS_60 0 2.8365874644341179e-06

GC_7_61 ref NI_7 NS_61 0 9.5375204351962245e-08

GC_7_62 ref NI_7 NS_62 0 2.5078512893506210e-05

GC_7_63 ref NI_7 NS_63 0 -1.4690120494583320e-08

GC_7_64 ref NI_7 NS_64 0 -3.3621817515436921e-02

GC_7_65 ref NI_7 NS_65 0 -5.0852847813760878e-04

GC_7_66 ref NI_7 NS_66 0 9.0034258861561634e-06

GC_7_67 ref NI_7 NS_67 0 -5.1861384490033846e-07

GC_7_68 ref NI_7 NS_68 0 4.6085300454495457e-07

GC_7_69 ref NI_7 NS_69 0 3.0128929882798380e-06

GC_7_70 ref NI_7 NS_70 0 1.1760245248711076e-07

GC_7_71 ref NI_7 NS_71 0 2.4219723070312446e-05

GC_7_72 ref NI_7 NS_72 0 -6.7457955981601432e-08

GC_7_73 ref NI_7 NS_73 0 -4.0773037174243911e-04

GC_7_74 ref NI_7 NS_74 0 -1.3887278468721487e-04

GC_7_75 ref NI_7 NS_75 0 9.0070129665824979e-06

GC_7_76 ref NI_7 NS_76 0 -2.4188575926766450e-07

GC_7_77 ref NI_7 NS_77 0 7.4768252366538078e-07

GC_7_78 ref NI_7 NS_78 0 1.0032124338272774e-05

GC_7_79 ref NI_7 NS_79 0 3.4319673730175726e-07

GC_7_80 ref NI_7 NS_80 0 5.9247766015885496e-06

GC_7_81 ref NI_7 NS_81 0 -5.3955420824467007e-08

GC_7_82 ref NI_7 NS_82 0 -2.1692762893661691e-02

GC_7_83 ref NI_7 NS_83 0 6.3060244325795559e-04

GC_7_84 ref NI_7 NS_84 0 9.0129049628760080e-06

GC_7_85 ref NI_7 NS_85 0 4.8328423598039223e-07

GC_7_86 ref NI_7 NS_86 0 8.6287230362213454e-08

GC_7_87 ref NI_7 NS_87 0 -6.0498226280034106e-06

GC_7_88 ref NI_7 NS_88 0 -4.0456951087774112e-07

GC_7_89 ref NI_7 NS_89 0 1.4009214969117422e-05

GC_7_90 ref NI_7 NS_90 0 4.6074611306676819e-07

GD_7_1 ref NI_7 NA_1 0 4.0652484331754797e-04

GD_7_2 ref NI_7 NA_2 0 1.3849606921248763e-03

GD_7_3 ref NI_7 NA_3 0 -2.7688431280543001e-02

GD_7_4 ref NI_7 NA_4 0 3.8337132136778369e-02

GD_7_5 ref NI_7 NA_5 0 -8.8280354409097095e-03

GD_7_6 ref NI_7 NA_6 0 5.2778514611757373e-02

GD_7_7 ref NI_7 NA_7 0 -3.7579684494547133e-01

GD_7_8 ref NI_7 NA_8 0 1.6411948479884181e-01

GD_7_9 ref NI_7 NA_9 0 5.9271946388552198e-03

GD_7_10 ref NI_7 NA_10 0 7.9689551015241944e-02

*

* Port 8

VI_8 a_8 NI_8 0

RI_8 NI_8 ref 1.0000000000000000e+01

GC_8_1 ref NI_8 NS_1 0 -8.3328785078003328e-04

GC_8_2 ref NI_8 NS_2 0 9.7920179120611285e-05

GC_8_3 ref NI_8 NS_3 0 9.0166067328772064e-06

GC_8_4 ref NI_8 NS_4 0 -1.1972240605360232e-06

GC_8_5 ref NI_8 NS_5 0 1.1856682444337307e-07

GC_8_6 ref NI_8 NS_6 0 1.8810350983420403e-06

GC_8_7 ref NI_8 NS_7 0 2.1358983504161111e-07

GC_8_8 ref NI_8 NS_8 0 2.9598335832023117e-05

GC_8_9 ref NI_8 NS_9 0 -1.8202467305244519e-06

GC_8_10 ref NI_8 NS_10 0 2.6217819915342884e-04

GC_8_11 ref NI_8 NS_11 0 6.1305915814843996e-06

GC_8_12 ref NI_8 NS_12 0 9.0045112555313546e-06

GC_8_13 ref NI_8 NS_13 0 -1.3000935170316881e-06

GC_8_14 ref NI_8 NS_14 0 -6.7420022972776967e-07

GC_8_15 ref NI_8 NS_15 0 1.5969279291525944e-06

GC_8_16 ref NI_8 NS_16 0 6.3140605369857789e-08

GC_8_17 ref NI_8 NS_17 0 3.0100767414671035e-05

GC_8_18 ref NI_8 NS_18 0 4.0059224890390890e-07

GC_8_19 ref NI_8 NS_19 0 7.2615118140603166e-03

GC_8_20 ref NI_8 NS_20 0 -5.0210543662861754e-05

GC_8_21 ref NI_8 NS_21 0 9.0056956164157562e-06

GC_8_22 ref NI_8 NS_22 0 2.4211745584587891e-06

GC_8_23 ref NI_8 NS_23 0 4.7844295429195046e-07

GC_8_24 ref NI_8 NS_24 0 1.0803387283146933e-05

GC_8_25 ref NI_8 NS_25 0 3.0559821951672671e-07

GC_8_26 ref NI_8 NS_26 0 -9.3087561333639300e-07

GC_8_27 ref NI_8 NS_27 0 -3.8495585152810928e-07

GC_8_28 ref NI_8 NS_28 0 -9.7405602613883160e-03

GC_8_29 ref NI_8 NS_29 0 3.3738448096731088e-04

GC_8_30 ref NI_8 NS_30 0 9.0134172030788365e-06

GC_8_31 ref NI_8 NS_31 0 1.8572138827498723e-06

GC_8_32 ref NI_8 NS_32 0 4.7616997890102826e-07

GC_8_33 ref NI_8 NS_33 0 -8.9533501352535938e-06

GC_8_34 ref NI_8 NS_34 0 -7.1006594851413431e-07

GC_8_35 ref NI_8 NS_35 0 5.9793469596960945e-06

GC_8_36 ref NI_8 NS_36 0 -1.8547544166576565e-08

GC_8_37 ref NI_8 NS_37 0 3.7757459912143593e-03

GC_8_38 ref NI_8 NS_38 0 -1.9431943364829293e-04

GC_8_39 ref NI_8 NS_39 0 9.0065101448898475e-06

GC_8_40 ref NI_8 NS_40 0 2.4500748927323447e-06

GC_8_41 ref NI_8 NS_41 0 8.2563474868311866e-07

GC_8_42 ref NI_8 NS_42 0 1.0776774189346394e-05

GC_8_43 ref NI_8 NS_43 0 3.1600549760124448e-07

GC_8_44 ref NI_8 NS_44 0 4.3616727885520055e-06

GC_8_45 ref NI_8 NS_45 0 -2.2084847783170986e-07

GC_8_46 ref NI_8 NS_46 0 -1.4236559521248986e-02

GC_8_47 ref NI_8 NS_47 0 4.3083533860830775e-04

GC_8_48 ref NI_8 NS_48 0 9.0125014995673979e-06

GC_8_49 ref NI_8 NS_49 0 1.4265135194477999e-06

GC_8_50 ref NI_8 NS_50 0 2.1539325635600245e-07

GC_8_51 ref NI_8 NS_51 0 -6.1989416280953190e-06

GC_8_52 ref NI_8 NS_52 0 -4.0507089270896263e-07

GC_8_53 ref NI_8 NS_53 0 1.3900087141622027e-05

GC_8_54 ref NI_8 NS_54 0 2.0788666732169189e-07

GC_8_55 ref NI_8 NS_55 0 -3.3621817515436865e-02

GC_8_56 ref NI_8 NS_56 0 -5.0852847813761105e-04

GC_8_57 ref NI_8 NS_57 0 9.0034258861561617e-06

GC_8_58 ref NI_8 NS_58 0 -5.1861384490033909e-07

GC_8_59 ref NI_8 NS_59 0 4.6085300454494436e-07

GC_8_60 ref NI_8 NS_60 0 3.0128929882798359e-06

GC_8_61 ref NI_8 NS_61 0 1.1760245248710114e-07

GC_8_62 ref NI_8 NS_62 0 2.4219723070312446e-05

GC_8_63 ref NI_8 NS_63 0 -6.7457955981601869e-08

GC_8_64 ref NI_8 NS_64 0 -5.5862033626845907e-02

GC_8_65 ref NI_8 NS_65 0 -5.6964565374198754e-04

GC_8_66 ref NI_8 NS_66 0 9.0009777103730491e-06

GC_8_67 ref NI_8 NS_67 0 -4.1458606901396592e-07

GC_8_68 ref NI_8 NS_68 0 5.7984537375799887e-07

GC_8_69 ref NI_8 NS_69 0 3.2171359382140742e-06

GC_8_70 ref NI_8 NS_70 0 1.0576342606470915e-07

GC_8_71 ref NI_8 NS_71 0 2.3415070639413175e-05

GC_8_72 ref NI_8 NS_72 0 -1.2333284151109414e-07

GC_8_73 ref NI_8 NS_73 0 1.4375950819301144e-04

GC_8_74 ref NI_8 NS_74 0 -1.7372743303921759e-04

GC_8_75 ref NI_8 NS_75 0 9.0068304091978800e-06

GC_8_76 ref NI_8 NS_76 0 2.4468544039420126e-06

GC_8_77 ref NI_8 NS_77 0 9.6889750956982396e-07

GC_8_78 ref NI_8 NS_78 0 1.0750901877579634e-05

GC_8_79 ref NI_8 NS_79 0 3.4811111330523899e-07

GC_8_80 ref NI_8 NS_80 0 5.7257318857884128e-06

GC_8_81 ref NI_8 NS_81 0 -6.8587458813847266e-08

GC_8_82 ref NI_8 NS_82 0 -2.1702078770299060e-02

GC_8_83 ref NI_8 NS_83 0 6.3861488295847957e-04

GC_8_84 ref NI_8 NS_84 0 9.0134760173507876e-06

GC_8_85 ref NI_8 NS_85 0 1.8593460801986451e-06

GC_8_86 ref NI_8 NS_86 0 1.5648078711265933e-07

GC_8_87 ref NI_8 NS_87 0 -6.4944521566393150e-06

GC_8_88 ref NI_8 NS_88 0 -3.8649745501323108e-07

GC_8_89 ref NI_8 NS_89 0 1.3531068663928303e-05

GC_8_90 ref NI_8 NS_90 0 4.4448921551877474e-07

GD_8_1 ref NI_8 NA_1 0 4.0771928372518442e-04

GD_8_2 ref NI_8 NA_2 0 -1.3192226213819124e-03

GD_8_3 ref NI_8 NA_3 0 -3.0762727937316107e-02

GD_8_4 ref NI_8 NA_4 0 3.4362172378454924e-02

GD_8_5 ref NI_8 NA_5 0 -1.1249709020994746e-02

GD_8_6 ref NI_8 NA_6 0 5.1842726999448974e-02

GD_8_7 ref NI_8 NA_7 0 1.6411948479884159e-01

GD_8_8 ref NI_8 NA_8 0 -3.6735414392415044e-01

GD_8_9 ref NI_8 NA_9 0 4.4338066267715047e-03

GD_8_10 ref NI_8 NA_10 0 7.9513368928699799e-02

*

* Port 9

VI_9 a_9 NI_9 0

RI_9 NI_9 ref 1.0000000000000000e+01

GC_9_1 ref NI_9 NS_1 0 -5.0302668975741021e-03

GC_9_2 ref NI_9 NS_2 0 2.2390301019291933e-04

GC_9_3 ref NI_9 NS_3 0 9.0198063392198828e-06

GC_9_4 ref NI_9 NS_4 0 -1.8742380972260081e-05

GC_9_5 ref NI_9 NS_5 0 2.9625665916699445e-06

GC_9_6 ref NI_9 NS_6 0 5.6139050859731403e-06

GC_9_7 ref NI_9 NS_7 0 7.3392732479095316e-08

GC_9_8 ref NI_9 NS_8 0 7.1672759455379916e-06

GC_9_9 ref NI_9 NS_9 0 -3.2161832621759753e-07

GC_9_10 ref NI_9 NS_10 0 -1.0808550191781882e-02

GC_9_11 ref NI_9 NS_11 0 2.2115128389801322e-04

GC_9_12 ref NI_9 NS_12 0 9.0049581092356892e-06

GC_9_13 ref NI_9 NS_13 0 -1.9890592830976059e-05

GC_9_14 ref NI_9 NS_14 0 -9.0872149630590269e-07

GC_9_15 ref NI_9 NS_15 0 4.7967578446840125e-06

GC_9_16 ref NI_9 NS_16 0 4.0432944218195370e-07

GC_9_17 ref NI_9 NS_17 0 7.3729627976287754e-06

GC_9_18 ref NI_9 NS_18 0 4.8324483084344154e-08

GC_9_19 ref NI_9 NS_19 0 2.2571873715636456e-02

GC_9_20 ref NI_9 NS_20 0 -4.1898501197431436e-04

GC_9_21 ref NI_9 NS_21 0 8.9929582270792386e-06

GC_9_22 ref NI_9 NS_22 0 4.3377352610311502e-05

GC_9_23 ref NI_9 NS_23 0 2.0292595030045561e-06

GC_9_24 ref NI_9 NS_24 0 3.3910680940182088e-05

GC_9_25 ref NI_9 NS_25 0 3.6138895022277320e-07

GC_9_26 ref NI_9 NS_26 0 9.5068276684950635e-08

GC_9_27 ref NI_9 NS_27 0 -5.7073145020128769e-07

GC_9_28 ref NI_9 NS_28 0 2.1931882924622606e-03

GC_9_29 ref NI_9 NS_29 0 -3.8718520063720635e-05

GC_9_30 ref NI_9 NS_30 0 9.0192242042872595e-06

GC_9_31 ref NI_9 NS_31 0 2.5161891876443357e-05

GC_9_32 ref NI_9 NS_32 0 6.3123338673152949e-07

GC_9_33 ref NI_9 NS_33 0 -2.8229643808002400e-05

GC_9_34 ref NI_9 NS_34 0 -1.1034939228437578e-06

GC_9_35 ref NI_9 NS_35 0 1.5095149560273720e-06

GC_9_36 ref NI_9 NS_36 0 -4.1178066131937172e-07

GC_9_37 ref NI_9 NS_37 0 2.0741788398399175e-02

GC_9_38 ref NI_9 NS_38 0 -1.0526219675052022e-03

GC_9_39 ref NI_9 NS_39 0 8.9940481511069240e-06

GC_9_40 ref NI_9 NS_40 0 4.5359743165954994e-05

GC_9_41 ref NI_9 NS_41 0 2.6923209303201263e-06

GC_9_42 ref NI_9 NS_42 0 3.3851062797887202e-05

GC_9_43 ref NI_9 NS_43 0 2.3298284685613105e-07

GC_9_44 ref NI_9 NS_44 0 1.2341213804704555e-06

GC_9_45 ref NI_9 NS_45 0 -4.3519147750590867e-07

GC_9_46 ref NI_9 NS_46 0 -1.3925280502172491e-02

GC_9_47 ref NI_9 NS_47 0 5.4550706141284950e-04

GC_9_48 ref NI_9 NS_48 0 9.0169493465309305e-06

GC_9_49 ref NI_9 NS_49 0 1.8575919234558078e-05

GC_9_50 ref NI_9 NS_50 0 -4.1555089519211989e-08

GC_9_51 ref NI_9 NS_51 0 -1.9489365244197628e-05

GC_9_52 ref NI_9 NS_52 0 -5.7581258501876334e-07

GC_9_53 ref NI_9 NS_53 0 3.3835481488918338e-06

GC_9_54 ref NI_9 NS_54 0 -1.3547580006848209e-08

GC_9_55 ref NI_9 NS_55 0 -4.0773037174245315e-04

GC_9_56 ref NI_9 NS_56 0 -1.3887278468721390e-04

GC_9_57 ref NI_9 NS_57 0 9.0070129665824979e-06

GC_9_58 ref NI_9 NS_58 0 -2.4188575926764253e-07

GC_9_59 ref NI_9 NS_59 0 7.4768252366540682e-07

GC_9_60 ref NI_9 NS_60 0 1.0032124338272783e-05

GC_9_61 ref NI_9 NS_61 0 3.4319673730173921e-07

GC_9_62 ref NI_9 NS_62 0 5.9247766015885436e-06

GC_9_63 ref NI_9 NS_63 0 -5.3955420824466782e-08

GC_9_64 ref NI_9 NS_64 0 1.4375950819300745e-04

GC_9_65 ref NI_9 NS_65 0 -1.7372743303921707e-04

GC_9_66 ref NI_9 NS_66 0 9.0068304091978800e-06

GC_9_67 ref NI_9 NS_67 0 2.4468544039420337e-06

GC_9_68 ref NI_9 NS_68 0 9.6889750956984959e-07

GC_9_69 ref NI_9 NS_69 0 1.0750901877579642e-05

GC_9_70 ref NI_9 NS_70 0 3.4811111330522591e-07

GC_9_71 ref NI_9 NS_71 0 5.7257318857884255e-06

GC_9_72 ref NI_9 NS_72 0 -6.8587458813853831e-08

GC_9_73 ref NI_9 NS_73 0 -4.1425287562941671e-02

GC_9_74 ref NI_9 NS_74 0 -1.3919153072805958e-03

GC_9_75 ref NI_9 NS_75 0 8.9866975809361527e-06

GC_9_76 ref NI_9 NS_76 0 4.5221041521223098e-05

GC_9_77 ref NI_9 NS_77 0 3.1516818345190192e-06

GC_9_78 ref NI_9 NS_78 0 3.3683767746150050e-05

GC_9_79 ref NI_9 NS_79 0 1.8144499326059408e-07

GC_9_80 ref NI_9 NS_80 0 1.5043606320199037e-06

GC_9_81 ref NI_9 NS_81 0 -3.3792490092663778e-07

GC_9_82 ref NI_9 NS_82 0 -2.6386308285233088e-02

GC_9_83 ref NI_9 NS_83 0 1.0254586077999412e-03

GC_9_84 ref NI_9 NS_84 0 9.0180624326382666e-06

GC_9_85 ref NI_9 NS_85 0 2.4335653268062583e-05

GC_9_86 ref NI_9 NS_86 0 -3.9093271414702207e-07

GC_9_87 ref NI_9 NS_87 0 -2.0349195541961039e-05

GC_9_88 ref NI_9 NS_88 0 -6.6230560085089572e-07

GC_9_89 ref NI_9 NS_89 0 3.2179114992299669e-06

GC_9_90 ref NI_9 NS_90 0 3.0286402899999217e-07

GD_9_1 ref NI_9 NA_1 0 1.6615060594218824e-02

GD_9_2 ref NI_9 NA_2 0 4.2441749921709564e-02

GD_9_3 ref NI_9 NA_3 0 -8.8950824702832498e-02

GD_9_4 ref NI_9 NA_4 0 -8.7325356282882630e-03

GD_9_5 ref NI_9 NA_5 0 -6.3365427706893948e-02

GD_9_6 ref NI_9 NA_6 0 4.7273353442178888e-02

GD_9_7 ref NI_9 NA_7 0 5.9271946388552718e-03

GD_9_8 ref NI_9 NA_8 0 4.4338066267715160e-03

GD_9_9 ref NI_9 NA_9 0 -4.0887545770434064e-01

GD_9_10 ref NI_9 NA_10 0 8.9728901464716793e-02

*

* Port 10

VI_10 a_10 NI_10 0

RI_10 NI_10 ref 1.0000000000000000e+01

GC_10_1 ref NI_10 NS_1 0 -1.6061220581368239e-02

GC_10_2 ref NI_10 NS_2 0 2.5103826054070509e-04

GC_10_3 ref NI_10 NS_3 0 9.0258318610652600e-06

GC_10_4 ref NI_10 NS_4 0 -9.2864546088353079e-06

GC_10_5 ref NI_10 NS_5 0 4.6625219837504312e-07

GC_10_6 ref NI_10 NS_6 0 -3.3236262873932414e-06

GC_10_7 ref NI_10 NS_7 0 -6.2224219727727848e-07

GC_10_8 ref NI_10 NS_8 0 1.7356044019333759e-05

GC_10_9 ref NI_10 NS_9 0 -1.0579662627130981e-06

GC_10_10 ref NI_10 NS_10 0 -1.7520331460230899e-02

GC_10_11 ref NI_10 NS_11 0 4.6644592360619219e-04

GC_10_12 ref NI_10 NS_12 0 9.0054193807990271e-06

GC_10_13 ref NI_10 NS_13 0 -9.6162138566756212e-06

GC_10_14 ref NI_10 NS_14 0 -2.2666460113404739e-07

GC_10_15 ref NI_10 NS_15 0 -2.8281573294987736e-06

GC_10_16 ref NI_10 NS_16 0 -5.9007938645064699e-07

GC_10_17 ref NI_10 NS_17 0 1.7406179993585272e-05

GC_10_18 ref NI_10 NS_18 0 6.4175417379562295e-07

GC_10_19 ref NI_10 NS_19 0 -1.4846281996922709e-02

GC_10_20 ref NI_10 NS_20 0 6.4319465304123983e-04

GC_10_21 ref NI_10 NS_21 0 9.0213655232443903e-06

GC_10_22 ref NI_10 NS_22 0 2.2862339942658149e-05

GC_10_23 ref NI_10 NS_23 0 4.9837497684773221e-07

GC_10_24 ref NI_10 NS_24 0 -2.0400091302394981e-05

GC_10_25 ref NI_10 NS_25 0 -6.5071962141298033e-07

GC_10_26 ref NI_10 NS_26 0 -9.7276054362740466e-07

GC_10_27 ref NI_10 NS_27 0 2.6608758379812165e-07

GC_10_28 ref NI_10 NS_28 0 4.0318179619208640e-04

GC_10_29 ref NI_10 NS_29 0 -1.0064266561274800e-04

GC_10_30 ref NI_10 NS_30 0 9.0046303639161613e-06

GC_10_31 ref NI_10 NS_31 0 1.1655623652954374e-05

GC_10_32 ref NI_10 NS_32 0 -5.1581920447099796e-07

GC_10_33 ref NI_10 NS_33 0 1.6917326089045514e-05

GC_10_34 ref NI_10 NS_34 0 1.1245452442394232e-06

GC_10_35 ref NI_10 NS_35 0 3.2905726603533608e-06

GC_10_36 ref NI_10 NS_36 0 3.2135702612771846e-07

GC_10_37 ref NI_10 NS_37 0 -2.3873930621022089e-02

GC_10_38 ref NI_10 NS_38 0 9.6329391202183983e-04

GC_10_39 ref NI_10 NS_39 0 9.0196298954355712e-06

GC_10_40 ref NI_10 NS_40 0 2.4269407857979653e-05

GC_10_41 ref NI_10 NS_41 0 -8.3295863920146290e-08

GC_10_42 ref NI_10 NS_42 0 -2.0399445185749029e-05

GC_10_43 ref NI_10 NS_43 0 -5.9799080578710900e-07

GC_10_44 ref NI_10 NS_44 0 2.2909870623594054e-06

GC_10_45 ref NI_10 NS_45 0 3.2668031266109389e-07

GC_10_46 ref NI_10 NS_46 0 -7.0641256326004235e-03

GC_10_47 ref NI_10 NS_47 0 -5.0072181086261726e-04

GC_10_48 ref NI_10 NS_48 0 9.0033294948750455e-06

GC_10_49 ref NI_10 NS_49 0 8.1441773734861976e-06

GC_10_50 ref NI_10 NS_50 0 2.4714140064430358e-07

GC_10_51 ref NI_10 NS_51 0 1.1610745752638745e-05

GC_10_52 ref NI_10 NS_52 0 6.1476632416056415e-07

GC_10_53 ref NI_10 NS_53 0 7.9970297618602125e-06

GC_10_54 ref NI_10 NS_54 0 2.4497830741259352e-07

GC_10_55 ref NI_10 NS_55 0 -2.1692762893661656e-02

GC_10_56 ref NI_10 NS_56 0 6.3060244325795559e-04

GC_10_57 ref NI_10 NS_57 0 9.0129049628760063e-06

GC_10_58 ref NI_10 NS_58 0 4.8328423598036513e-07

GC_10_59 ref NI_10 NS_59 0 8.6287230362150469e-08

GC_10_60 ref NI_10 NS_60 0 -6.0498226280034174e-06

GC_10_61 ref NI_10 NS_61 0 -4.0456951087774625e-07

GC_10_62 ref NI_10 NS_62 0 1.4009214969117403e-05

GC_10_63 ref NI_10 NS_63 0 4.6074611306677301e-07

GC_10_64 ref NI_10 NS_64 0 -2.1702078770299029e-02

GC_10_65 ref NI_10 NS_65 0 6.3861488295847892e-04

GC_10_66 ref NI_10 NS_66 0 9.0134760173507859e-06

GC_10_67 ref NI_10 NS_67 0 1.8593460801986288e-06

GC_10_68 ref NI_10 NS_68 0 1.5648078711262614e-07

GC_10_69 ref NI_10 NS_69 0 -6.4944521566393226e-06

GC_10_70 ref NI_10 NS_70 0 -3.8649745501322463e-07

GC_10_71 ref NI_10 NS_71 0 1.3531068663928320e-05

GC_10_72 ref NI_10 NS_72 0 4.4448921551876712e-07

GC_10_73 ref NI_10 NS_73 0 -2.6386308285233442e-02

GC_10_74 ref NI_10 NS_74 0 1.0254586077999507e-03

GC_10_75 ref NI_10 NS_75 0 9.0180624326382666e-06

GC_10_76 ref NI_10 NS_76 0 2.4335653268062607e-05

GC_10_77 ref NI_10 NS_77 0 -3.9093271414697569e-07

GC_10_78 ref NI_10 NS_78 0 -2.0349195541961029e-05

GC_10_79 ref NI_10 NS_79 0 -6.6230560085091827e-07

GC_10_80 ref NI_10 NS_80 0 3.2179114992299652e-06

GC_10_81 ref NI_10 NS_81 0 3.0286402899999302e-07

GC_10_82 ref NI_10 NS_82 0 -6.4594533478451233e-02

GC_10_83 ref NI_10 NS_83 0 -1.0660909913113403e-03

GC_10_84 ref NI_10 NS_84 0 8.9911653049222036e-06

GC_10_85 ref NI_10 NS_85 0 1.0437603406379908e-05

GC_10_86 ref NI_10 NS_86 0 7.5575595208938042e-07

GC_10_87 ref NI_10 NS_87 0 1.2105137516333903e-05

GC_10_88 ref NI_10 NS_88 0 4.5812299240997361e-07

GC_10_89 ref NI_10 NS_89 0 7.9799693143995328e-06

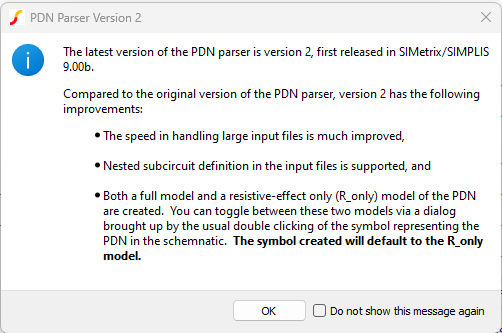

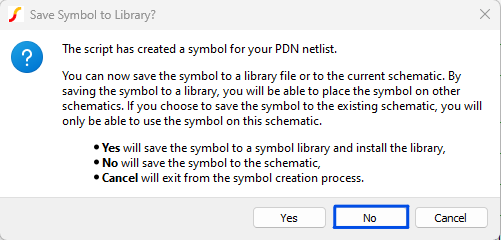

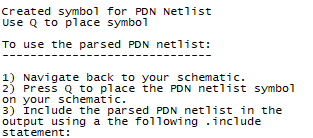

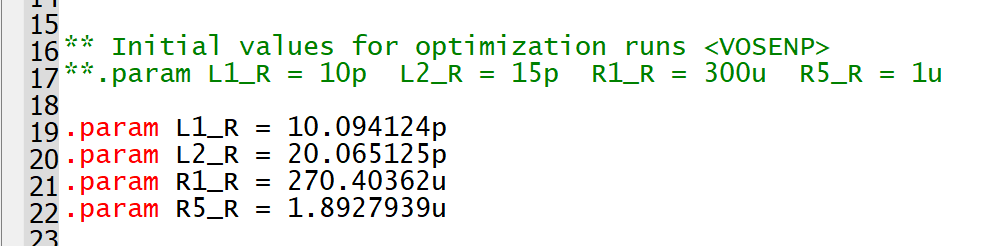

GC_10_90 ref NI_10 NS_90 0 3.8597065700773107e-09